1130 Computing System

IBM Field Engineering

Field Engineering Theory of Operation (Manual of Instruction)

| Branch Office: |      |  |

|----------------|------|--|

|                | 5    |  |

| Department:    | <br> |  |

| Address:       | <br> |  |

### PREFACE

The IBM Theory of Operation (Manual of Instruction) <u>1130</u> Computing System contains information on the 1131 Central Processing Unit and Console, and the attachment circuits for the Input/Output units: Console Printer, Console Keyboard, and Disk File Storage. Descriptions of the attachment circuits for the IBM 1442 Card Read-Punch, IBM 1132 Printer, IBM 1134 Paper Tape Reader, IBM 1055 Paper Tape Punch and IBM 1627 Plotter, are found in the <u>Field</u> Engineering Manual of Instruction 1130 Computing System-Features.

Information regarding the Input/Output units may be found in the manual of instruction for each unit as listed in the Bibliography, Appendix A.

The users of this manual are cautioned that specifications are subject to change at any time and without prior notice by IBM. Wiring diagrams (logics) at the engineering change level of that specific machine are included in each machine shipment.

This manual form 227-5978-2 is a major revision of form 227-5978-1. The latter is made obsolete by this revision.

Copies of this and other IBM publications can be obtained through IBM Branch Offices. Comments concerning the contents of this publication may be addressed to: IBM, Product Publications Department, San Jose, Calif. 95114

© 1966 by International Business Machines Corporation

# CONTENTS

•

| CHAPTER 1 INTRODUCTION                                            | 1.1  |

|-------------------------------------------------------------------|------|

| DESCRIPTION OF SYSTEM                                             | 1.1  |

| 1.1 Machine Language                                              | 1.3  |

| 1.1.1 Character Code                                              | 1.3  |

| 1.1.2 Instruction Format                                          | 1.3  |

| 1.1.3 Data Format                                                 | 1.4  |

| 1.2 Stored Program Concept                                        | 1.4  |

| 1.2.1 Program Location                                            | 1.5  |

| DATA FLOW AND CORE STORAGE ADDRESSING                             | 1.6  |

| 1.3 Data Flow                                                     | 1.6  |

| 1.4 Core Storage                                                  | 1.6  |

| 1.5 Core Storage Read and Write                                   | 1.6  |

| 1.5.1 Reading Out of Core Storage                                 | 1.8  |

| 1.5.2 Writing Into Core Storage                                   | 1.8  |

| 1.6 Data Distribution                                             | 1.8  |

| CONSOLE                                                           | 1.9  |

| 1.7 Console Function                                              | 1.9  |

| 1.8 Console Display Panel                                         | 1.9  |

| 1.8.1 Indicator Displays                                          | 1.9  |

| 1.8.2 Mode Switch                                                 | 1.10 |

| 1.8.3 Emergency Power Off Switch                                  | 1.10 |

| 1.9 Console Printer.                                              | 1.10 |

| 1.9.1 Bit Switch Data Input                                       | 1.10 |

| 1.10 Console Keyboard                                             | 1.10 |

| 1.10.1 Status Indicator Panel.                                    | 1.11 |

| 1.10.2 Control Switch Panel                                       | 1.12 |

| 1.10.3 Data Input Keyboard                                        | 1.12 |

| 1.10.4 Keyboard Function Keys                                     | 1.12 |

| • •                                                               | 1.14 |

| 1.10.5         Keyboard Operation           1.11         CE Panel | 1.14 |

|                                                                   |      |

| INSTRUCTION TIME                                                  | 1.16 |

| 1.12 Instruction Cycles                                           | 1.16 |

| 1.13 Instruction Cycle 1 (I-1)                                    | 1.16 |

| 1.13.1 Single-Word Format Without Indexing                        |      |

| (F = 0, Tag = 00)                                                 | 1.18 |

| 1.13.2 Single-Word Format With Indexing                           |      |

| $(F = 0, Tag \neq 00)$                                            | 1.18 |

| 1.13.3 Double-Word Format (F = 1)                                 | 1.19 |

| 1.14 Instruction Cycle 2 (I-2)                                    | 1.19 |

| 1.15 Indexing Cycle (I-X)                                         | 1.19 |

| 1.16 Indirect Addressing Cycle (I-A)                              | 1.20 |

| EXECUTION TIME                                                    | 1.22 |

| 1.17 Execution Cycles.                                            | 1.22 |

| 1.17.1 E-Cycle Flip-Flops                                         | 1.23 |

| 1.17.2 Auxiliary Flip-Flops                                       | 1.24 |

| PROGRAMMING                                                       | 1.25 |

| 1.18 Development of A Program                                     | 1.25 |

| 1.19 Compute $X + Y = Z$                                          | 1,25 |

| 1.20 Load Factors Into Core Storage                               | 1.25 |

| 1.21 Loading A Program Into Core Storage                          | 1.26 |

| 1.22 Execution of A Program                                       | 1.26 |

| 1.22.1 Execute Program                                            | 1.26 |

| 1.23 Display Result                                               | 1.27 |

| 1.23.1 Display Sum                                                | 1.27 |

| 1.24 Program Repetition                                           | 1.27 |

| 1.24.1 Enter Different Factors                                    | 1.27 |

|                                                                   |      |

2

| DISK STORAGE         1. 25 Disk Storage Description         1. 25.1 Disk Storage Unit         1. 25.2 Disk Assembly         1. 25.3 Access Mechanism         1. 25.4 Disk Organization and Capacity         1. 25.5 Disk Storage Timing | 1.27<br>1.28<br>1.28<br>1.28<br>1.28<br>1.28<br>1.28<br>1.29<br>1.30<br>1.30 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 1.25 Disk Storage Description         1.25.1 Disk Storage Unit         1.25.2 Disk Assembly         1.25.3 Access Mechanism         1.25.4 Disk Organization and Capacity         1.25.5 Disk Storage Timing                            | 1.28<br>1.28<br>1.28<br>1.28<br>1.28<br>1.29<br>1.30                         |

| 1.25.1 Disk Storage Unit1.25.2 Disk Assembly1.25.3 Access Mechanism1.25.4 Disk Organization and Capacity1.25.5 Disk Storage Timing                                                                                                      | 1,28<br>1,28<br>1,28<br>1,29<br>1,30                                         |

| 1. 25.2 Disk Assembly1. 25.3 Access Mechanism1. 25.4 Disk Organization and Capacity1. 25.5 Disk Storage Timing                                                                                                                          | 1.28<br>1.28<br>1.29<br>1.30                                                 |

| 1.25.3 Access Mechanism1.25.4 Disk Organization and Capacity1.25.5 Disk Storage Timing                                                                                                                                                  | 1.28<br>1.29<br>1.30                                                         |

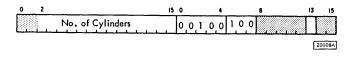

| 1.25.4 Disk Organization and Capacity1.25.5 Disk Storage Timing                                                                                                                                                                         | 1.29<br>1.30                                                                 |

| 1.25.5 Disk Storage Timing                                                                                                                                                                                                              | 1.30                                                                         |

|                                                                                                                                                                                                                                         |                                                                              |

|                                                                                                                                                                                                                                         | 1.30                                                                         |

|                                                                                                                                                                                                                                         |                                                                              |

|                                                                                                                                                                                                                                         |                                                                              |

| CHAPTER 2 FUNCTIONAL UNITS                                                                                                                                                                                                              | 2.1                                                                          |

|                                                                                                                                                                                                                                         | 2.1                                                                          |

|                                                                                                                                                                                                                                         | 2.1                                                                          |

|                                                                                                                                                                                                                                         | 2.3                                                                          |

|                                                                                                                                                                                                                                         | 2.4                                                                          |

| •                                                                                                                                                                                                                                       | 2.6                                                                          |

|                                                                                                                                                                                                                                         | 2.6                                                                          |

|                                                                                                                                                                                                                                         | 2.6                                                                          |

|                                                                                                                                                                                                                                         | 2.6                                                                          |

|                                                                                                                                                                                                                                         | 2.6                                                                          |

|                                                                                                                                                                                                                                         | 2.6                                                                          |

|                                                                                                                                                                                                                                         | 2.6                                                                          |

|                                                                                                                                                                                                                                         | 2.6                                                                          |

|                                                                                                                                                                                                                                         | 2.6                                                                          |

|                                                                                                                                                                                                                                         | 2.0                                                                          |

|                                                                                                                                                                                                                                         | 2.8                                                                          |

| 3                                                                                                                                                                                                                                       | 2.8<br>2.12                                                                  |

|                                                                                                                                                                                                                                         | 2.17                                                                         |

| 5, <u>5</u> , <u>5</u>                                                                                                                                                | 2.17                                                                         |

|                                                                                                                                                                                                                                         | 2.18                                                                         |

|                                                                                                                                                                                                                                         | 2.21                                                                         |

|                                                                                                                                                                                                                                         | 2.21                                                                         |

|                                                                                                                                                                                                                                         | 2.21                                                                         |

|                                                                                                                                                                                                                                         | 2.21                                                                         |

|                                                                                                                                                                                                                                         |                                                                              |

|                                                                                                                                                                                                                                         | 2.26                                                                         |

|                                                                                                                                                                                                                                         | 2.26                                                                         |

|                                                                                                                                                                                                                                         | 2.20                                                                         |

|                                                                                                                                                                                                                                         | -                                                                            |

|                                                                                                                                                                                                                                         | 2.26                                                                         |

| · · ··································                                                                                                                                                                                                  | 2.27                                                                         |

|                                                                                                                                                                                                                                         | 2.28                                                                         |

| 2.6.2 Interrupt Controls                                                                                                                                                                                                                | 2.29                                                                         |

| 2.6.3 Disk Storage Attachment                                                                                                                                                                                                           | 2.33                                                                         |

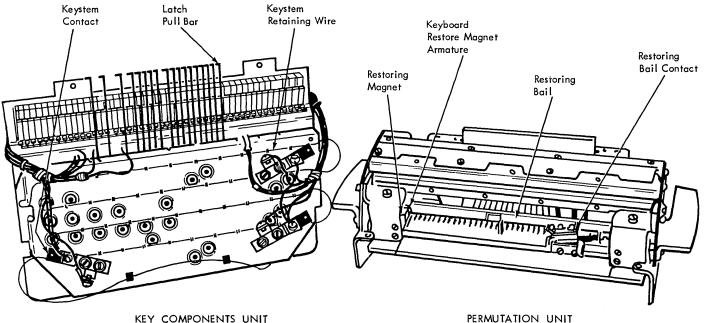

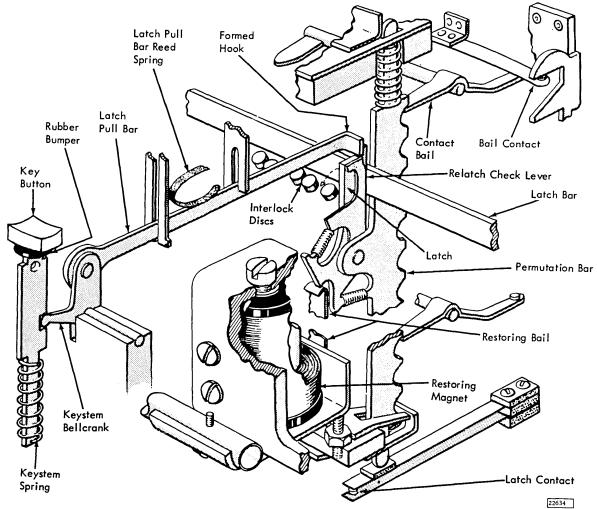

| 2.7 Console Keyboard                                                                                                                                                                                                                    | 2.35                                                                         |

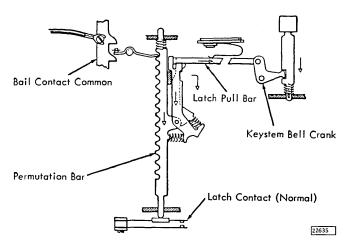

| 2.7.1 Keyboard Mechanics                                                                                                                                                                                                                | 2.35                                                                         |

| 2.7.2 Bail and Latch Contacts                                                                                                                                                                                                           | 2.37                                                                         |

| 2.7.3 Keyboard Restoring Components                                                                                                                                                                                                     | 2.39                                                                         |

| 2.7.4 Keyboard Interlocks                                                                                                                                                                                                               | 2.40                                                                         |

| 2.7.5 Keyboard Electrical Functions                                                                                                                                                                                                     | 2.41                                                                         |

| CHAPTER 3 THEORY OF OPERATION                                                                                                                                                                                                           | 3.1                                                                          |

|                                                                                                                                                                                                                                         | 3.1                                                                          |

| 3.1 Load Accumulator                                                                                                                                                                                                                    | 3.1                                                                          |

| 3.2 Load Double                                                                                                                                                                                                                         | 3.1                                                                          |

| 3.3 Store Accumulator                                    | 3.2  |

|----------------------------------------------------------|------|

| 3.4 Store Double                                         | 3.2  |

| 3.5 Load Index                                           | 3.2  |

| 3.6 Store Index                                          | 3.3  |

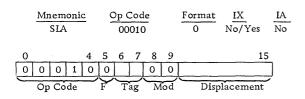

| 3.7 Load Status                                          | 3.3  |

| 3.8 Store Status                                         | 3.3  |

| BRANCH AND SKIP OPERATIONS                               | 3.4  |

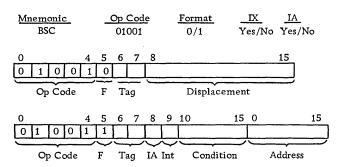

| 3.9 Branch or Skip On Condition                          | 3.4  |

| 3.9.1 Circuit Description-One Word Instruction - BSC     | 3.6  |

| 3.9.2 Circuit Description - Two Word Instruction - BSC.  | 3.6  |

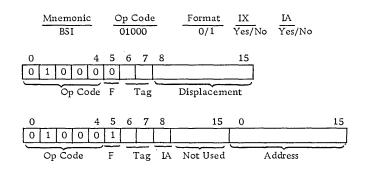

| 3.10 Branch and Store Instruction Register               | 3.7  |

| 3.10.1 Circuit Description - One Word Instruction - BSI. | 3.7  |

| 3.10.2 Circuit Description - Two Word Instruction-BSI .  | 3.7  |

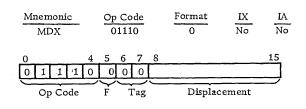

| 3.11 Modify Index, F = 0, Tag = 00                       | 3.8  |

| 3.12 Modify Index, $F = 0$ , Tag $\neq 00$               | 3.8  |

| 3.13 Modify Index, F = 1, Tag = 00                       | 3.8  |

| 3.14 Modify Index, $F = 1$ , Tag $\neq 00$ , IA = 0      | 3.9  |

| 3.15 Modify Index, $F = 1$ , Tag $\neq 00$ , IA = 1      | 3.9  |

| SHIFT OPERATIONS                                         | 3.10 |

| 3.16 Shift Left A                                        | 3.10 |

| 3.17 Shift Left A & Q                                    | 3.10 |

| 3.18 Shift Left and Count ACC                            | 3.11 |

| 3.19 Shift Left and Count A & Q                          | 3.12 |

| 3.20 Shift Right A                                       | 3.12 |

| 3.21 Shift Right A & Q                                   | 3.12 |

| 3.22 Rotate Right A & Q                                  | 3.13 |

| ARITHMETIC OPERATIONS                                    | 3.14 |

| 3.23 Add                                                 | 3.14 |

| 3.24 Double Add                                          | 3.14 |

| 3.25 Subtract                                            | 3.15 |

| 3.26 Double Subtract                                     | 3.15 |

| 3.27 Multiply                                            | 3.16 |

| 3.28 Divide                                              | 3.17 |

| LOGICAL OPERATIONS                                       | 3.18 |

| 3.29 Logical And                                         | 3.18 |

| 3.30 Logical Or                                          | 3.18 |

| 3.31 Logical Exclusive Or                                | 3.19 |

| INPUT/OUTPUT OPERATIONS                                  | 3.20 |

| 3.32 X10 Instruction                                     | 3.20 |

| 3.32.1 I/O Control Commands                              | 3.20 |

| 3.32.2 Input/Output Termination                          | 3.22 |

| 3.32.3 Input/Output Interrupts                           | 3.22 |

|                                                          |      |

| 3.32.4    | Interrupt Level Status Word             | 3,22   |

|-----------|-----------------------------------------|--------|

|           | Device Status Word                      | 3.22   |

| 3.33 I/O  | Attachments                             | 3.22   |

|           | I/O Interface                           | 3.23   |

|           | ect Program Controlled Operation        | 3.23   |

|           | Read/Write Function                     | 3.23   |

|           | Control Function                        | 3.23   |

|           | Sense Function                          | 3.24   |

|           | Busy Condition                          | 3.24   |

|           | sole Printer - Keyboard                 | 3.24   |

|           | sole Printer                            | 3.24   |

|           | Printer Functional Description          | 3.24   |

|           | Console Printer Programming             | 3.25   |

|           | I/O Control Commands (IOCC)             | 3.25   |

|           | Console Printer Operation               | 3.26   |

|           | sole Keyboard                           | 3.27   |

|           | Console Keyboard Functional Description | 3.27   |

| 3.37.2    | Keyboard Operating Procedures.          | 3.28   |

|           | Console Keyboard Programming            | 3.29   |

|           | I/O Control Commands (IOCC)             | 3,29   |

|           | Keyboard Read Operation                 | 3.29   |

| 3.37.6    | Keyboard Sense Operation                | 3.30   |

| 3.38 Con  | sole Bit Switches                       | 3.30   |

|           | Bit Switch Functional Description       | 3,30 - |

| 3.38.2    | Programming                             | 3.31   |

| 3.38.3    | I/O Control Commands (IOCC)             | 3.31   |

| 3.38.4    | Bit Switch Read Operation               | 3.31   |

| 3.39 Con  | nbined Control                          | 3.31   |

| 3.40 Disk | Storage Operations                      | 3.32   |

| 3.40.1    | I/O Control Commands (IOCC)             | 3.32   |

|           | Circuit Descriptions                    | 3.33 - |

|           |                                         |        |

|           |                                         |        |

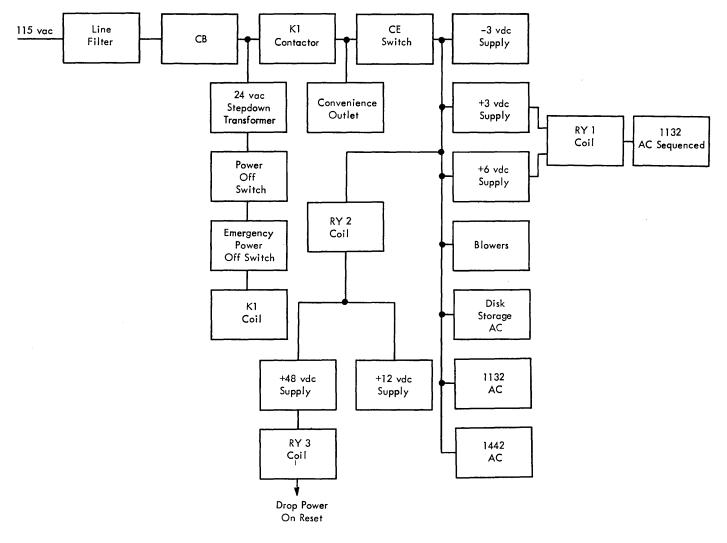

|           | 4 POWER SUPPLY                          | 4.1    |

|           | Voltages and Sequencing                 | 4.1    |

| 4.2 DC V  | /oltages                                | 4.1    |

| 4.5 50 0  | ycie                                    | 4.1    |

| APPENDIX  | A. BIBLIOGRAPHY                         | A. 1   |

|           |                                         |        |

| INDEX • • |                                         | I. 1   |

### DESCRIPTION OF SYSTEM

- The IBM 1130 is a solid state system composed of a Central Processing Unit (including core storage and disk storage) and I/O Units.

- The Central Processing Unit (CPU) has Console Keyboard and Console Printer.

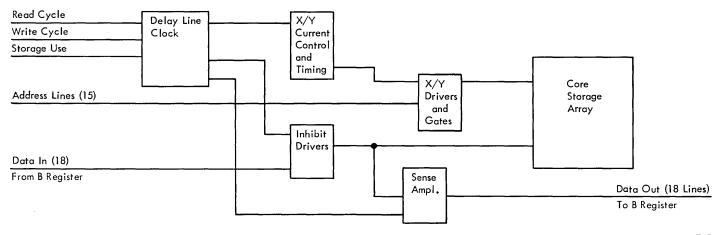

- Core storage can contain 4,096 or 8,192 words.

- Each 16-bit core storage word can be addressed.

- Alphameric and special characters may be stored.

- The program is stored in core storage.

- Program instructions may be sequential or non-sequential.

- 1130 is an add-to-accumulator computer.

- Addition, subtraction, multiplication and division are accomplished by a special adder circuit.

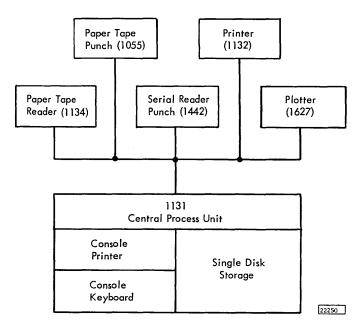

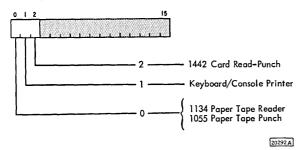

The IBM 1130 Computing System is a solid-state electronic computer system, designed specifically for technical applications. The IBM 1134 Paper Tape Reader, the IBM 1055 Paper Tape Punch, the IBM 1627 Plotter, the IBM 1132 Printer, and the IBM 1442 Card Read Punch are input-output units available for various customer applications (Figure 1-1). Information on these input-output units is included in the IBM Customer Engineering Manuals of Instruction for each unit.

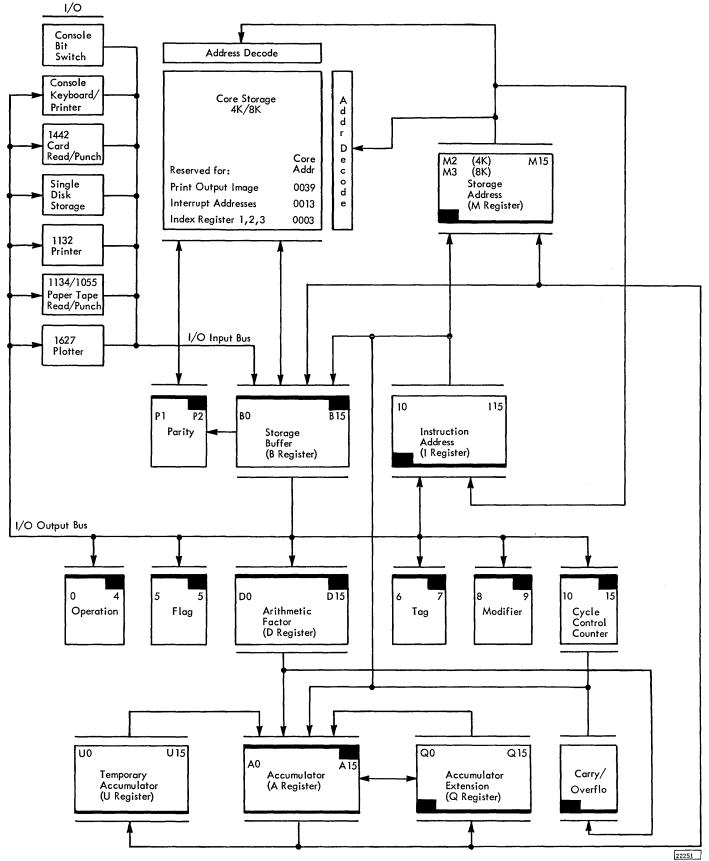

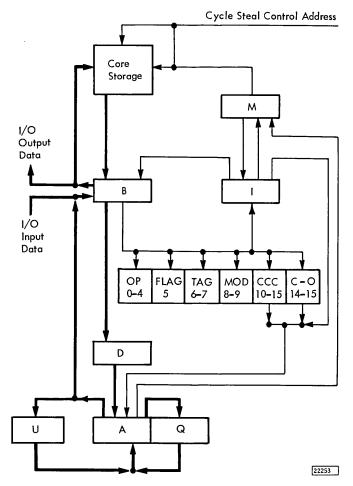

The IBM 1131 Central Processing Unit contains the logic circuitry, the console panel, the console keyboard, console printer, and the disk storage drive (Models 2A and 2B only). Figure 1-2 shows the data flow of the system.

Data and instructions entered into the system are placed in core storage as 16-bit binary words. Each word in core storage can be addressed individually by a 4-digit decimal address and can store one or more characters of information. Core storage addresses extend from 0000 to 4095 for 4,096 words of core storage and from 0000 to 8191 for 8,192 words of core storage. This addressing system enables selection of any word or group of words within core storage. The system processes binary information only. All alphabetic, numerical and special characters are coded and decoded by programming for input/output operations. For example, in order to print information on the 1132 Printer, data must be coded in extended binary coded decimal coding.

The system is capable of performing 24 basic operations. Each operation is specified by an instruction which can be one or two words long. The instruction contains an operation code, data which generates an effective address, and/or modifying bits. Instructions comprising a program are normally stored in consecutive locations in core storage and executed sequentially. However, the sequence of operations may be altered at any point in the program by conditional skip and branch instructions. Conditional skip and branch instructions make logical decisions by performing tests on indicators set by the computer or the program.

Figure 1-1. 1130 System Configurator

<sup>\*</sup> NOTE: The illustrations in this manual have a code number in the lower corner. This is a publishing control number and is not related to the subject matter.

Figure 1-2. 1130 System Data Flow

\_\_\_\_\_

The 1130 is an add-to-accumulator computer. That is, a word of core storage is added to the contents of an accumulator to develop a result.

Addition, subtraction, multiplication, and division operations are accomplished by the binary logic adder circuits of the accumulator.

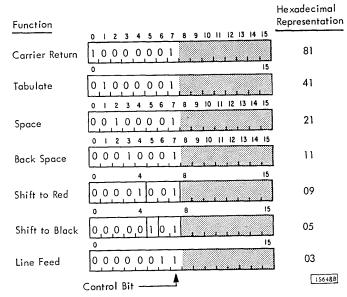

The 1130 console contains control keys, switches, an indicator panel, a console keyboard and a console printer. The control keys and switches are used by the operator to communicate with and control operation of the system. The indicator panel provides a visual indication of the contents of various registers and the status of control circuitry within the computer. The console keyboard and console bit switches are used for manual entry of data and instructions into core storage. The console printer prints serially at the rate of 15.5 characters per second.

Information is entered into the system by the console bit switches, the console keyboard, the IBM 1134 Paper Tape Reader, or the IBM 1442 Card Read Punch. Output data is recorded by the console printer, the IBM 1442 Card Read Punch, the IBM 1627 Plotter, IBM 1055 Paper Tape Punch, or the IBM 1132 Printer. Information also may be entered into or removed from the system by way of the replaceable IBM 2315 Disk Cartridge.

When the computer is reading from, or writing on, and input/output device, each character received from, or sent to, the input-output device is represented in core storage as a single 16-bit word.

# 1.1 MACHINE LANGUAGE

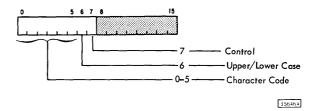

### 1.1.1 Character Code

- Data is stored, transferred, and processed in binary form.

- Each word is made up of a combination of binary bits.

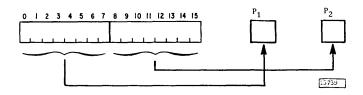

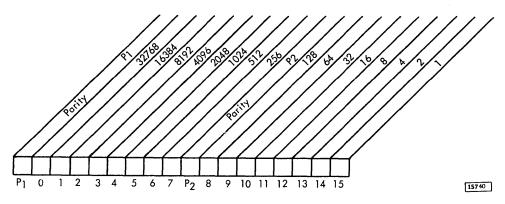

- Each core storage word has 18 bit positions: Bit 0 through bit 15 and two parity bits.

- Parity (P) bits are used to maintain an odd number of bits in each half word in core storage and the B register. Parity bit one maintains odd parity for bits 0-7, parity bit two for bits 8-15.

All data stored, transferred, or processed with the 1130 is represented in binary form. A number is represented by a particular combination of bits. The

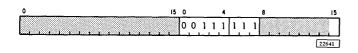

bit positions of each number consist of 16 data (B0 through B15) bits, and two parity (P) bits Figure 1-3). The decimal value of a word is the sum represented by the bits present in the data bit positions. A zero is represented by the two P bits. The digit 6 is represented by a bit 13 and a bit 14 plus both P bits; the digit 257 is represented by a bit 7 and a bit 15, no P bits (Figure 1-4).

The P bits are used for parity checking purposes. Each half word within core storage must consist of an odd total number of bits, or a parity error will be indicated. The P bit is present in a digit when the number of bits present in the numerical bit positions consists of an even number of bits.

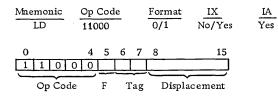

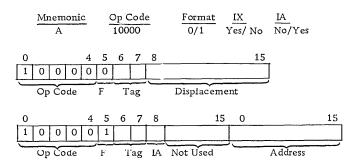

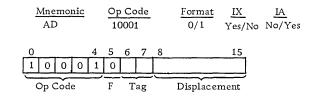

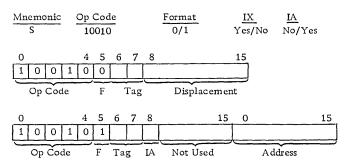

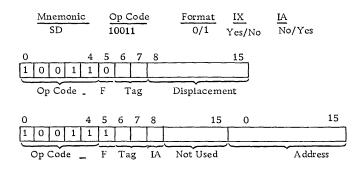

#### 1.1.2 Instruction Format

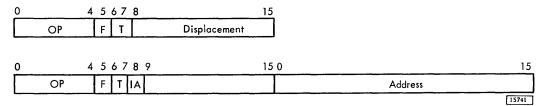

- Instructions contain one or two 16-bit words.

- The operation code specifies what is to be done.

- The effective address specifies the word to be processed.

- Single word instructions have: A 5 bit operation code and 11 controlling bits which form an effective core address or which control the operation. Figure 1-5.

- Two word instructions have: A 5 bit operation code, a 16 bit core address, and modifier bits which provide specific control to the operation.

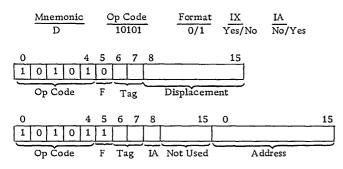

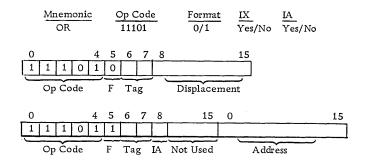

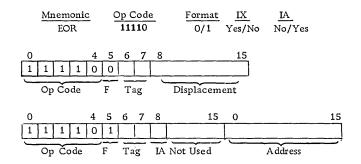

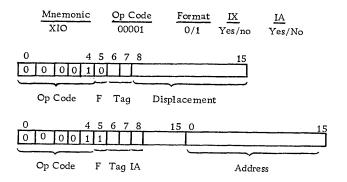

The operation code consists of 5 binary bits which specify the operation to be performed. Figure 1-6 is a chart of basic operation codes and their associated mnemonics.

The functions of the modifier parts of an instruction depend upon the particular operation to be performed. The address part of an instruction represents the core storage address of a single or double word, or of an instruction, or of another address. It may also contain special information

Figure 1-3. Bit Positions

Figure 1-4. Bit Configuration - Numeric

required by the operation such as how far to shift or on what condition to branch or skip. The specific use of the address and modifier parts of the instruction are described with each operation.

#### 1.1.3 Data Format

- Data may be arranged in core storage to form data tables.

- A data table is a number of consecutive words related to input/output operations.

- Data tables are normally processed, starting with the high-order word (low numbered core storage position).

Data tables can be of any length from one core storage position to the maximum number of positions in core storage. Data in core storage can be defined as words or tables.

A word occupies only one core storage position and has its own specific address.

A table in core storage consists of one or more words of data related to input/output operations. On output operations, a table in core storage is addressed at the position which occupies the lowestnumbered core storage position of the table. Tables are processed serially into successively higher core storage positions. Input operations enter data into core storage starting at the addressed position and continuing into successively higher core storage locations until terminated by the program or by an "end of transmission" signal from the device.

- 1.2 STORED PROGRAM CONCEPT

- A program in a series of instructions that cause the system to perform a function.

- The working instructions are stored in core storage.

- Instructions are read from core storage into registers for decoding to control the system operation.

- During the time that a program is being executed additional instructions and data may be entered into core storage from cards, disk storage, or paper tape.

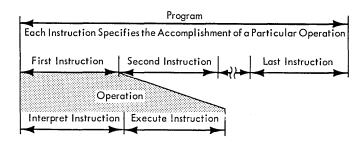

To solve a problem or to process data, a programmer selects, from the instructions which the system is capable of performing, those instructions which are required to accomplish the desired results. The series of instructions, which designate the operations to be performed and the sequence in which they are to be performed, is called a program. Because the instructions comprising a program are written into core storage from an input device and read from core storage for interpretation and execution, the 1130 is called a stored program computer.

Figure 1-5. Instruction Formats

| Binary | Mnemonic |                                      |

|--------|----------|--------------------------------------|

| 00000* | WAIT     | Wait                                 |

| 00001  | хю       | Execute I/O Instruction              |

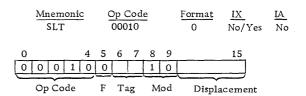

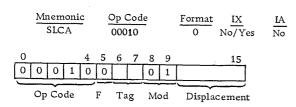

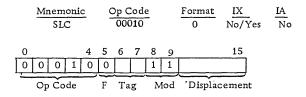

| 00010  | SLA      | Shift Left A                         |

| 00010  | SLT      | Shift Left A and Q                   |

| 00010  | SLCA     | Shift Left and Count A               |

| 00010  | SLC      | Shift Left and Count A and Q         |

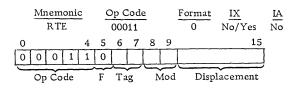

| 00011  | RTE      | Rotate Right A and Q                 |

| 00011  | SRA      | Shift Right A                        |

| 00011  | SRT      | Shift Right A and Q                  |

| 00100  | LDS      | Load Status                          |

| 00101  | STS      | Store Status                         |

| 01000  | BSI      | Branch and Store Instruction Counter |

| 01001  | BSC      | Branch or Skip On Condition          |

| 01100  | LDX      | Load Index                           |

| 01101  | STX      | Store Index                          |

| 01110  | MDX      | Modify Index and Skip                |

| 10000  | A        | Add                                  |

| 10001  | AD       | Double Add                           |

| 10010  | S        | Subtract                             |

| 10011  | SD       | Double Subtract                      |

| 10100  | м        | Multiply                             |

| 10101  | D        | Divide                               |

| 11000  | LD       | Load Accumulator                     |

| 11001  | LDD      | Double Load                          |

| 11010  | sto      | Store Accumulator                    |

| 11011  | STD      | Double Store                         |

| 11100  | AND      | Logical AND                          |

| 11101  | OR       | Logical OR                           |

| 11110  | EOR      | Logical Exclusive OR                 |

\* All unassigned Operation Codes are defined as Wait Operations.

Figure 1-6. 1130 Operation Codes

For interpretation by the computer, an instruction must be read from core storage into registers.

Instructions within a program are normally interpreted and executed sequentially; that is, execution of

Figure 1-7. Program

the first instruction is followed by interpretation and execution of the second instruction, etc. (Figure 1-7). However, this sequence can be altered by the use of branch instructions that direct the computer to an instruction location at a location other than the next sequential core storage location.

While a program is being executed, additional instructions and/or data may be read into core storage from an input device or read out of core storage into an output device.

The only distinction between instructions and data in core storage is the manner in which they are interpreted by the computer. If data is placed in core storage locations assigned to an instruction, the data will be acted upon as if it were an instruction. Conversely, the operation code or address part of an instruction may be modified by treating the instruction as data.

# 1.2.1 Program Location

Program instructions and data may be located anywhere in core storage. However, some blocks of core storage have assignments and should not be used for other uses unless they are not used for the assigned purpose. As shown in Figure 1-8, locations 0001 to 0003 are used as index registers, 0008-0013 for interrupt level address storage, and 0032-0039 for 1132 Printer print control.

|     | ndex | 0000 |    |    |    | terru |    | 0010 | 0010 |            | Printe | •  |     | 0000         |

|-----|------|------|----|----|----|-------|----|------|------|------------|--------|----|-----|--------------|

|     | 0002 |      | "  |    |    |       |    |      |      | 0032<br>// |        |    |     |              |

| XR1 | XR2  | XR3  | إر | L0 | LI | L2    | L3 | L4   | L5   | , 1<br>, , | 2      | 44 | 119 | 1 <b>2</b> 0 |

Levels

Figure 1-8. Core Storage Location Assignments

Registers

22252

Table

### DATA FLOW AND CORE STORAGE ADDRESSING

#### 1.3 DATA FLOW

- Data is normally processed serially by word, parallel by bit.

- Instructions are executed by a series of machine cycles.

- Each machine cycle reads and writes an addressed core storage position.

The IBM 1130 System normally processes data serially by word, parallel by bit. The 18 bits which are read from core storage for each address are processed simultaneously under most conditions, but the bits can be processed individually in some operations.

Data is confined to core storage, the storage buffer (B) register, the arithmetic factor (D) register, the accumulator (A) register, the temporary accumulator (U) register, the accumulator extension (Q) register, and the input/output areas. Digits which are presented to other registers by the B register are used to develop core storage (CS) addresses or to control program execution (Figure 1-2).

Each instruction of a program is interpreted and executed by a series of machine cycles. A machine cycle consists essentially of: addressing core storage, reading out of a core storage location, and writing into a core storage location.

Digits read from core storage, that are used for addressing or control purposes, are set into registers from the B register within the cycle or are retained in the B register until the next cycle. Digits are presented to an output device from the B register or received from an input device through the B register within the machine cycle. Figure 1-9.

### 1.4 CORE STORAGE

- All core storage is housed within the IBM 1131 Central Processing Unit.

- 4,096 or 8,192 words of core storage are available.

- One 18-bit word is read on each machine cycle.

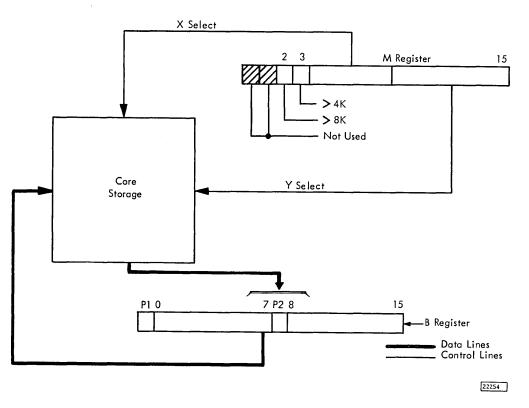

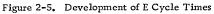

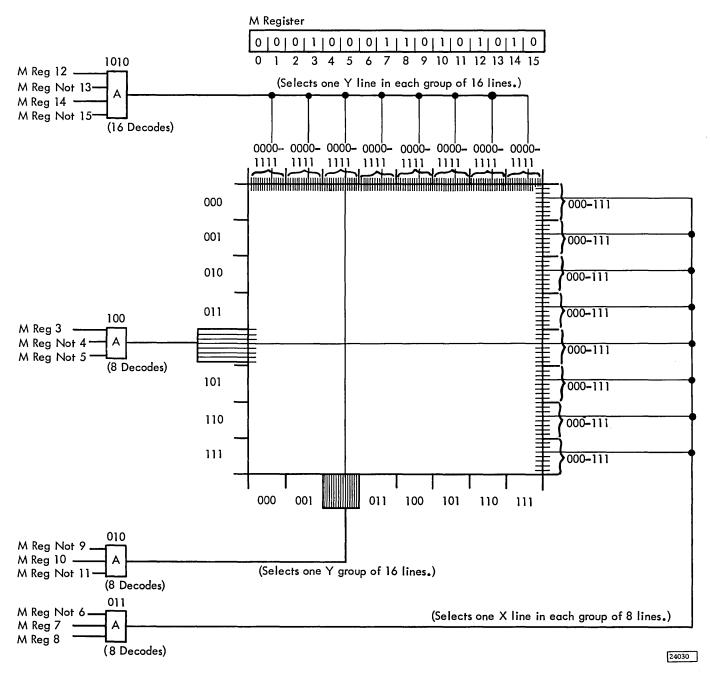

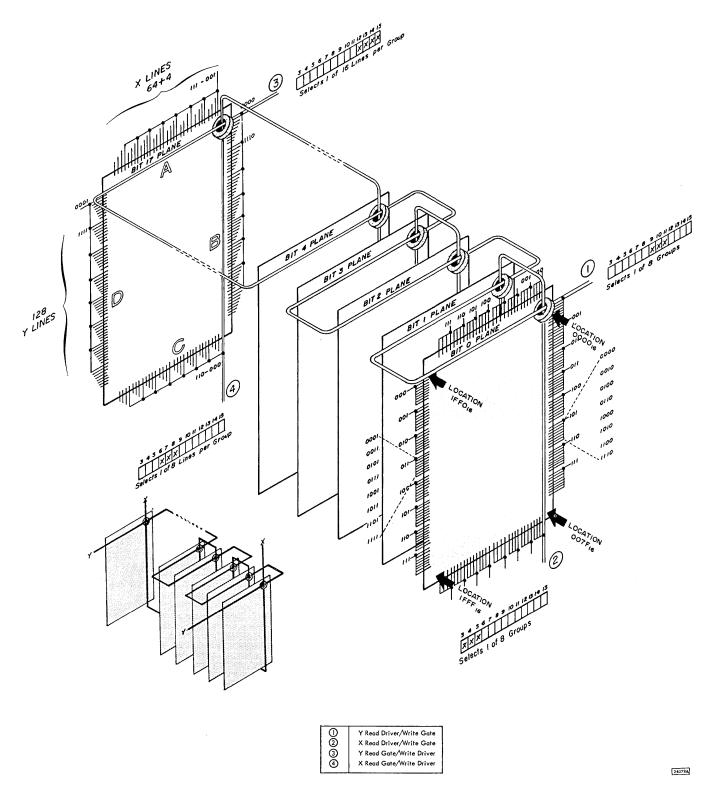

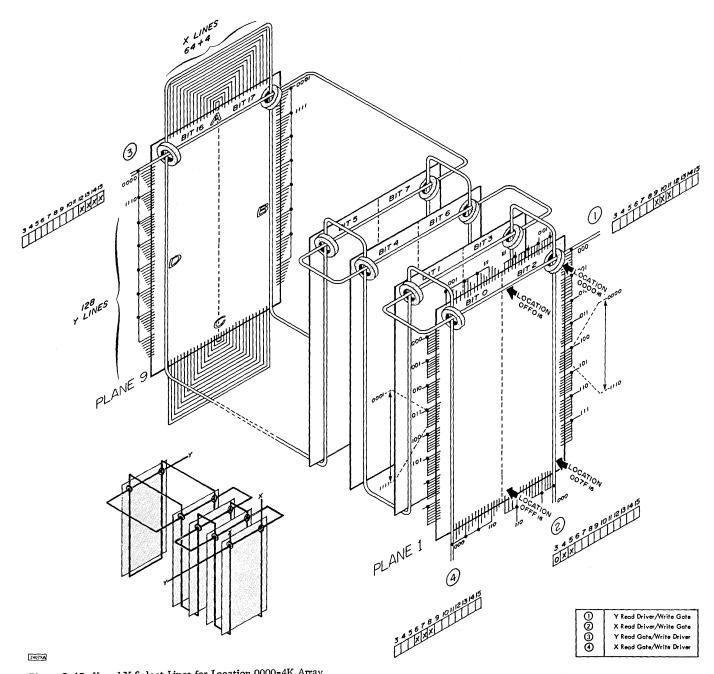

Core storage is addressed by means of two lines which select a single "column" of 18 cores (one core in the same position in each plane). Because each word in core storage consists of 18 bits, selecting

Figure 1-9. Data Flow

one column of 18 cores causes a full word to be read out each time core storage is addressed (Figure 1-10).

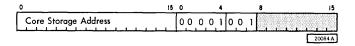

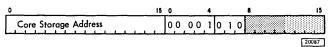

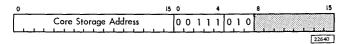

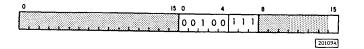

The core storage address is in the form of a 13 bit binary coded word. This address word is set into the storage address (M) register at the beginning of each machine cycle in which a new word is required from core.

With the installation of additional core storage, the addressing scheme is expanded to include circuitry which selects addresses greater than 4096.

#### 1.5 CORE STORAGE READ AND WRITE

- Words (16 bits) are read from core storage into the storage buffer (B) register.

- P bit flip-flop's (F F's) are not part of the B register.

Figure 1-10. Addressing Core Storage

- Words are written into core storage from the B register and the P bit F F's.

- Read-out of core storage is destructive, therefore regeneration is required.

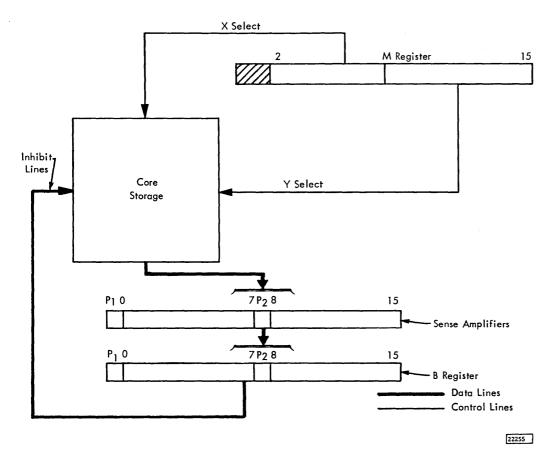

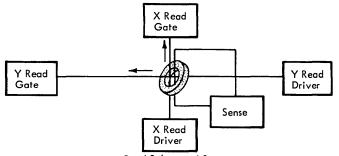

The 18 bits which are read out of memory are sensed by sense amplifiers which in turn set FF's in the B register and the P FF's. The B register is a 16position register with one FF for each position in the word (Figure 1-11).

Read out of cores is destructive; therefore, to retain the word it must be written back into the cores from which it was read. This is accomplished by retaining the word in the B register. Whatever is in the B register at the end of a machine cycle has automatically been written into core storage.

### 1.5.1 Reading Out of Core Storage

When core storage is addressed, the B register F F's are turned off, and the core storage output is sensed by the sense amplifiers. The output of each sense amplifier is associated with a F F in the B register. Therefore, each sense amplifier that senses an

output from core storage turns on its associated B register FF. Each sense amplifier that does not sense an output from core storage does not affect its associated B register FF.

Parity (odd number of bits) of the word in the B register is checked during each machine cycle after the register is set from the sense amplifiers.

### 1.5.2 Writing Into Core Storage

The word that is in the B register at the end of the machine cycle is automatically set into core storage at the location specified by the M register.

When a new word is to replace a word previously read out of core storage, the old word is destroyed as the new word is set into the B register.

#### 1.6 DATA DISTRIBUTION

After the 18-bit word is read from core into the B register and P bit FF's, it is distributed to various control registers or the data (D) register as dictated by the operation code and machine cycle being used.

### CONSOLE

#### 1.7 CONSOLE FUNCTION

- The console is an integral part of the IBM 1311 Central Processing Unit.

- The console consists of the input keyboard, the output printer, and the display panel.

The input keyboard is used to enter data and instructions into core storage. Functions of the control switches and lights are described in this section. Functions of the data input keys are described in Chapter 3 Input/Output Operations.

The output printer is used to print out information that is in core storage. Functions of the printer attachment are described in Chapter 3 Input/ Output Operations, 3.36 Console Printer.

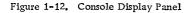

### 1.8 CONSOLE DISPLAY PANEL

- The contents of the registers within the computer are displayed on the console panel (Figure 1-12).

- Each bit in each register position is represented by a light.

- The light is on when the bit which it represents is present in the word displayed.

- The mode switch selects the operating mode of the system.

### 1.8.1 Indicator Displays

Instruction (I) Address Register: Consists of one row of 14 lamps. Each lamp displays the status of one flip-flop (FF) in the I register.

Storage (M) Address Register: Consists of one row of 14 lamps. Each lamp displays the status of one FF in the M register. Storage Buffer (B) Register: Consists of one row of 16 lamps. Each lamp indicates the status of one FF in the B register. At the end of each machine cycle the B register reflects the bits that were read into core storage on the cycle just completed.

Arithmetic Factor Register (D): Consists of one row of 16 lamps. Each lamp indicates the status of one FF in the D register.

Accumulator (A) Register: Consists of one row of 16 lamps. Each lamp indicates the status of one FF in the A register.

Accumulator Extension (Q) Register: Consists of one row of 16 lamps. Each lamp indicates the status of one FF in the Q register.

<u>Clock Timer (T)</u>: Consists of one row of 8 lamps. These lamps indicate the last clock step completed.

Machine Cycle (I and E): Consists of one row of 7 lamps. These lamps indicate the type of machine cycle in process when in single step mode. They indicate the machine cycle just completed when in any other mode.

X7: Indicates when X7 clock is active.

Parity  $(P_1, P_2)$ : Consists of two lamps. P<sub>1</sub> indicates parity for B register bits 0-7. P<sub>2</sub> indicates parity for B register bits 8-15.

<u>Control Flip-Flop's</u>: Consists of two rows of 7 lamps. These lamps indicate the status of various control FF's: add, AC-arith control, SC-shift control, AS-accumulator sign, TC-temporary carry, ZR-zero remainder, and W-wait operation.

<u>CE Lights</u>: Consists of two rows of 6 lamps. Each lamp can be wired by a CE to give a visual indication of any status condition in the machine.

|       | INSTRUCTION              | 2, 15 | то | τi | т2 | Т3 | T4 | т5          | T6 T7 | OPERATION<br>REGISTER    | 0  | 1  | 2  | 3  | 4  |   | ]       |

|-------|--------------------------|-------|----|----|----|----|----|-------------|-------|--------------------------|----|----|----|----|----|---|---------|

|       | STORAGE<br>ADDRESS       | 2 15  | II | 12 | IX | IA | EI | E2          | E3 X7 | OPERATION<br>FLAGS       | F5 | т6 | т7 | М8 | М9 |   | ]       |

| (EPO) | STORAGE<br>BUFFER        | 0 !5  | PI | P2 |    | w  |    | <b>b</b> bA | AC SC | INDEX<br>REGISTER        |    | 1  | 2  | 3  |    |   | SMC-    |

|       | ARITHMETIC<br>FACTOR     | 0 15  |    |    |    |    |    | AS          | TC ZR | INTERRUPT<br>LEVELS      | 0  | 1  | 2  | 3  | 4  | 5 | SS Load |

|       | ACCUMULATOR              | 0     | ł  | 2  | 3  | 4  | 5  | 6           |       | CYCLE CONTROL<br>COUNTER | 32 | 16 | 8  | 4  | 2  | I | ]       |

|       | ACCUMULATOR<br>EXTENSION | 0 15  | 7  | 8  | 9  | 10 | 11 | 12          |       | CONDITION                | с  |    | 0  |    |    |   | ]       |

22256

Operation (OP) Register: Consists of one row of 5 lamps. These lamps indicate the operation in process when in single step mode or single machine cycle mode. They indicate the operation just completed when in any other mode.

Operation Tags: Consists of one row of 5 lamps. These lamps indicate the status of the format, tag, and modifier registers.

Index Register: Consists of one row of 3 lamps. These lamps indicate index register address.

Interrupt Levels: Consists of one row of 5 lamps. These lamps indicate the interrupt levels that are active.

Cycle Control Counter (CCC): Consists of one row of 6 lamps. These lamps indicate the binary value contained in the CCC.

Condition Register: Consists of one row of 2 lamps. These lamps indicate the status of the carry FF and the overflow FF.

### 1.8.2 Mode Switch

The mode switch selects one of 7 operating modes.

<u>Single Step (SS)</u>: With the mode switch set to SS, each depression of the start key causes the 1131 clock to advance one step (for example from T1 to T2).

Single Machine Cycle (SMC): With the mode switch set to SMC, each depression of the start key causes the 1131 to advance one machine cycle (for example from I-1 to I-2).

Interrupt Run (INT RUN): With the mode switch set to INT RUN, pressing the start key causes the 1131 to advance through its stored program. A level 5 interrupt occurs after each mainline program instruction is completed.

Program Run (RUN): With the mode switch set to RUN, pressing the start key causes the 1131 to advance through its stored program.

Single Instruction (SI): With the mode switch set to SI, each depression of the start key causes the 1131 to interpret and execute a single instruction. Display (DISP) Core Storage: With the mode switch set to DISP, pressing the start key will display (in the B register) the core storage word at the location specified by the address in the instruction address register and advance IAR by one.

Load Core Storage (LOAD): With the mode switch set to LOAD, pressing the start key will load the data from the console entry switches (on the 1053 printer) into core storage at the location specified by the address in the instruction address register.

Pressing the load IAR CE switch in this mode transfers the data in the bit switches into the Iregister.

#### 1.8.3 Emergency Power OFF Switch

This pull type switch drops power to the system and must be reset by the CE.

#### 1.9 CONSOLE PRINTER

- Mechanically an IBM 1053 Printer.

- 16 console entry switches are on the front panel.

- Console entry switches are used to enter data, instructions and addresses.

- See Chapter 3 for a description of the printing functions.

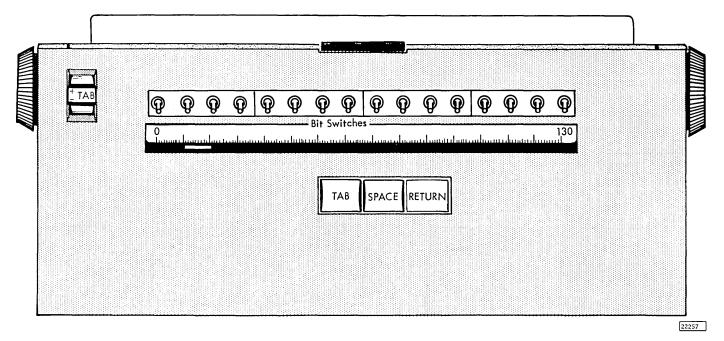

The console printer (Figure 1-13) is located directly beneath the console display panel. It is an IBM 1053 Printer with 16 bit (console entry) switches mounted on the front panel. Each switch is directly related to a bit position of a core storage word.

These switches are used in conjunction with the mode switch on the display panel and the control switches on the console keyboard.

#### 1.9.1 Bit Switch Data Input

To enter data from the bit switches under program operation the console/keyboard switch must be in the console position. The CPU program selects the bit switches, (Area 7), and reads the data from the bit switches on to the I/O input bus and sets it into the B register.

Figure 1-13. Console Printer

- 1.10 CONSOLE KEYBOARD

- Basically an 029 Card Punch keyboard.

- Contains 8 status indicator lamps.

- Contains 7 control switches.

- See Chapter 3 for a description of the keyboard data input functions.

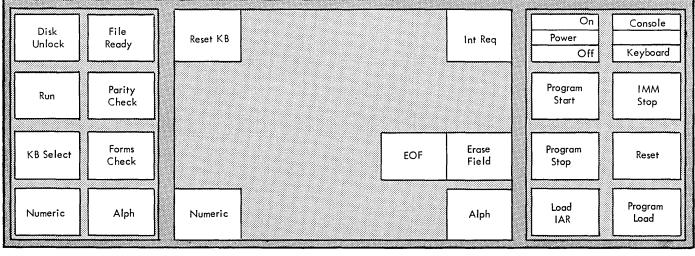

The console keyboard (Figure 1-14) is located directly in front of the console printer. It is made up of an IBM 029 Card Punch keyboard, a status indicator lamp panel, and a control-switch panel.

1.10.1 Status Indicator Panel

Forms Check: this lamp is turned on when the last form has been detected by the console printer forms contact.

Status Indicator Panel

Data Input Keyboard

**Control Switch Panel**

22258

Figure 1-14. Console Keyboard

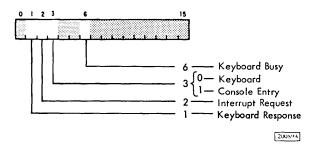

Keyboard Select: This lamp is turned on by a programmed instruction (X10 Control) that requests input data from the keyboard.

Ready: When on, this lamp indicates that the system is in a "ready-to-operate" status.

Parity Check: This lamp is turned on when a parity error (even number of bits) is detected in the word in the B register.

<u>Alphabetic</u>: This lamp indicates that the keyboard is in alphabetic (lower case) shift. The letters and symbols which appear in the bottom portion of the keyboard character keys can be entered when the keyboard is in alphabetic shift.

Numeric: This lamp indicates that the keyboard is in numeric (upper case) shift. The letters and symbols which appear on the top portion of the keyboard character keys can be entered only when the keyboard is in numeric shift.

Run: This lamp is turned on when the system is executing a program in run mode.

File Ready: This lamp is turned on when the disk cartridge is loaded and ready to operate.

#### 1.10.2 Control Switch Panel.

<u>Power:</u> This two position toggle switch controls system power.

<u>Console/Keyboard</u>: This two position toggle switch indicates the source of the console input data to the program. The source is either the keyboard or the console entry switches.

Start: Pressing this pushbutton switch causes the machine to take one clock step or machine cycle and continue to take additional cycles if required by the setting of the mode switch.

Stop: Pressing this pushbutton switch causes an immediate stop of the CPU, interrupt, and cycle-stealing cycles. I/O devices will complete the cycle they are in when STOP is pressed. Data from I/O devices will be lost if they are operating at the time the stop key is pressed. A complete program restart is normally required.

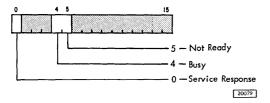

Program Stop: Pressing this pushbutton switch causes the CPU and I/O devices to "cycle down" to a stop. The "cycle down" procedure is accomplished by turning on the program stop bit in the console device status word and causing a level 5 interrupt. After the program has satisfied all interrupts for levels 1 through 4 (all I/O devices except the console) it enters a routine for level 5. Because the console is the only unit on level 5, the device status word for the console can be sensed without interrogating the interrupt level status word. The program stop bit in the device status word directs the program to a wait loop that blocks all mainline operations until the console operator intervenes.

<u>Reset</u>: Pressing this pushbutton switch resets all machine registers except the M and U registers, cycle FF, control FF, and status indicators. The reset key is inoperative while the machine is run mode.

Load IAR: Pressing this pushbutton switch causes the contents of the bit switches to be placed in the instruction address register.

Program Load: Pressing this pushbutton switch causes a program to be loaded into core storage.

If the system has an IBM 1442 Card Read Punch, the card data is loaded into storage locations 0000-0079 and the CPU will go to location 0000 for the next instruction.

If the system does not have an IBM 1442, the load circuit is added to the IBM 1054 Paper Tape Reader attachment circuits. When the program load key is pressed, the program is loaded into core storage starting at location 0000. Only tape channels 4, 3, 2, and 1 are used. These bits are used in groups of four to form 16-bit words. When a channel 5 punch is read, the read operation is stopped and the CPU will go to 0000 for the next instruction.

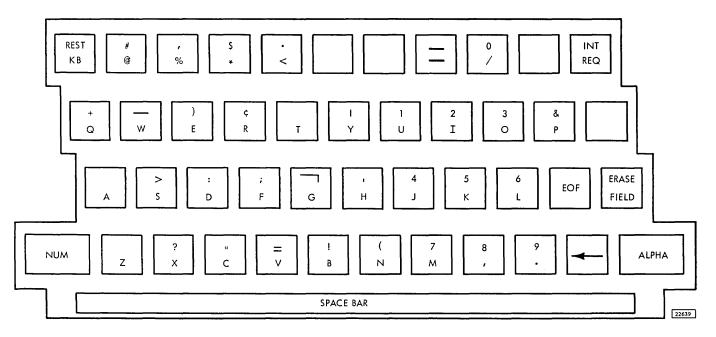

### 1.10.3 Data Input Keyboard. (Figures 1-15 and 1-16)

Keyboard entries are not automatically printed unless the CPU is programmed to provide an output of the entry on the printer. To enter data from the keyboard, the CPU program must select the keyboard (Area 1), with the console/keyboard switch in the keyboard position, and the select light on. The

Figure 1-15. Console Keyboard Entry Keys

Figure 1-16. Console Keyboard Bit Entry

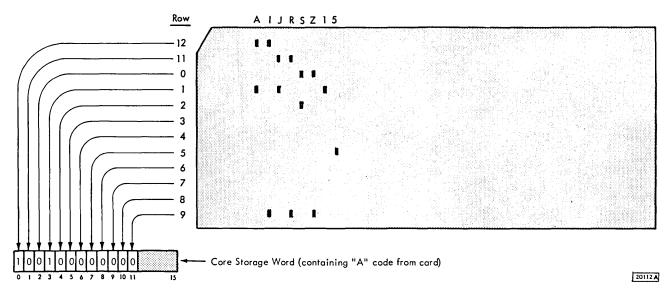

keyboard emits a coded character for each key struck by the operator. These characters are related to IBM card coding. Striking the A character key places bits in positions 0 and 3 of the CPU word; striking the I character key places bits in positions 0 and 11 of the word; etc. See Figure 1-16. The data from the keyboard is entered on the I/O input bus and set into the B register.

# 1.10.4 Keyboard Function Keys

Interrupt Request: This key initiates a keyboard restore and causes an interrupt in the CPU.

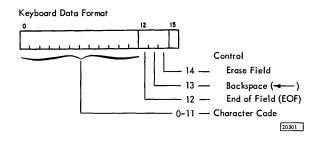

End of Field (EOF): When the CPU reads in response to this key, a word containing a 12 bit only is placed in memory. Analysis of this word allows the program to determine that no further characters are to be sent in this message.

Backspace (-): When the CPU reads in response to this key, a word containing a 13 bit only is placed in memory. Analysis of this word allows the program to determine that the last character received is to be replaced by the next character to be entered.

Erase Field: When the CPU reads in response to this key, a word containing a 14 bit only is placed in memory. Analysis of this word allows the program to determine that the message being entered is to be deleted and replaced by a corrected message.

<u>Mode</u>: They are two mode keys: numeric (upper case shift) and alphabetic (lower case shift). These keys place the keyboard in the indicated mode. The keyboard remains in the selected mode until changed by the operator. If the numbers or symbols which appear on the top portion of the keys are desired, the keyboard must be placed in numeric mode.

<u>Reset Keyboard</u>: This key allows the operator to restore the keys if they become locked.

### 1.10.5 Keyboard Operation

The following procedure describes a typical use of the keyboard.

- 1. The operator presses the keyboard request key with the console/keyboard switch in the keyboard position, to initiate a request interrupt and place the keyboard in a restore status.

- 2. The CPU honors the request interrupt.

- 3. When the keyboard has been determined to be the device that caused the interrupt, the CPU issues a control command to select the keyboard. When the keyboard is selected, the select light is turned on to signal the operator that a character can be entered.

- 4. When a character key is pressed, the keyboard initiates a service interrupt to the CPU.

- 5. In response to the service interrupt, the CPU performs a read command which enters the character into core storage and removes the keyboard from the selected status.

- 6. Before another character can be entered, the CPU stored program must issue another control command to select the keyboard.

If the CPU performs a read command when the keyboard is not selected, no bits are entered.

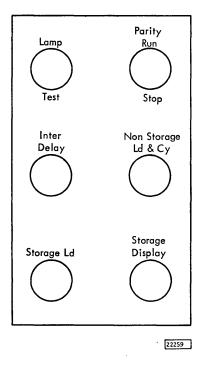

### 1.11 CE PANEL

The CE panel (Figure 1-17) is located under the right end of the console display panel and contains six switches.

Lamp Test: This switch lights all lamps on the display panel to check their operation.

Parity Run/Stop: This two position toggle switch is normally set to STOP. If the CE wishes the program to bypass a parity error for diagnostic purposes, this switch is set to RUN and the program continues to run even if a parity error is detected.

NOTE: The parity run/stop switch must be in STOP when the system is returned to the customer.

Interrupt Delay: This switch when on blocks setting of the interrupt FF's.

Non-Storage Load and Cycle: Pressing the start key with this switch on allows the information in the bit switches to enter the B register. Input and output of core storage is inhibited. Depending on the setting of the mode switch, a cycle or step is taken without changing storage. This operation allows the CE to check the operation of the CPU without changing data in core storage.

Storage Load: When this switch is on, the information in the bit switches is entered into core. Depending on the setting of the mode switch, one or all core positions will be changed. For example, to set all core storage positions to zero, set all bit switches off, set the mode switch to run, set the storage load switch on and press the start key. Parity checking is under control of the parity run/stop CE switch.

Storage Display: Pressing the start switch when this switch is on causes the information in core storage to be displayed in the B register. Parity checking is under control of the parity run/stop CE switch.

### INSTRUCTION TIME

### 1.12 INSTRUCTION CYCLES

- Instruction time (I cycles) interprets the instruction and develops an effective address (EA).

- Reads the instruction from the core storage location specified by the instruction address register.

- Six instruction types are used: Single-word format, without indexing. Single-word format, with indexing. Double-word format, without indexing, without indirect addressing. Double-word format, with indexing, without indirect addressing.

Double-word format, without indexing, with indirect addressing.

Double-word format, without indexing, with indirect addressing.

Double-word format, with indexing, with indirect addressing.

- Decodes the instruction format bit to determine whether the instruction is one or two words in length.

- Decodes the instruction tag bits to determine if the instruction is an indexing instruction.

- Decodes the instruction modifier bit to determine if the instruction has an indirect address.

- Instruction cycle 1 (I-1) is used by all instructions.

- Instruction cycle 2 (I-2) is used by all doubleword-format instructions.

- Indirect addressing cycle (I-A); is used by indirect addressing instructions.

- Indexing cycle (I-X) is used by indexing instructions.

- Reference Maintenance Diagrams: AA101, AA211, AA601.

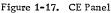

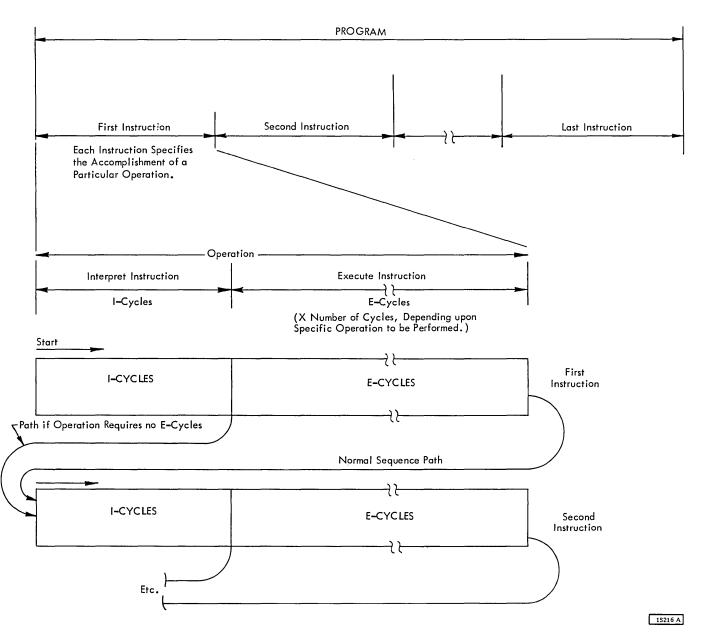

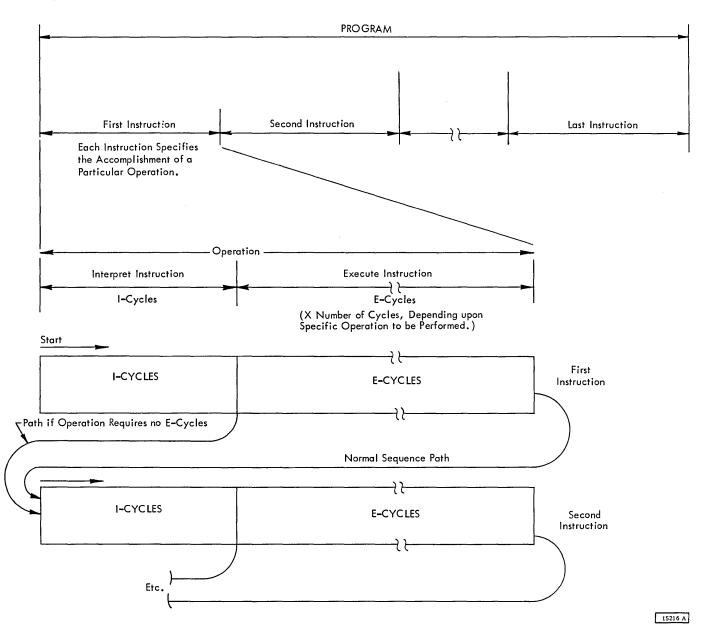

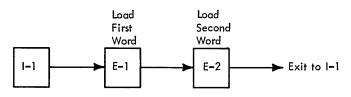

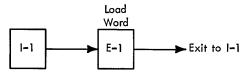

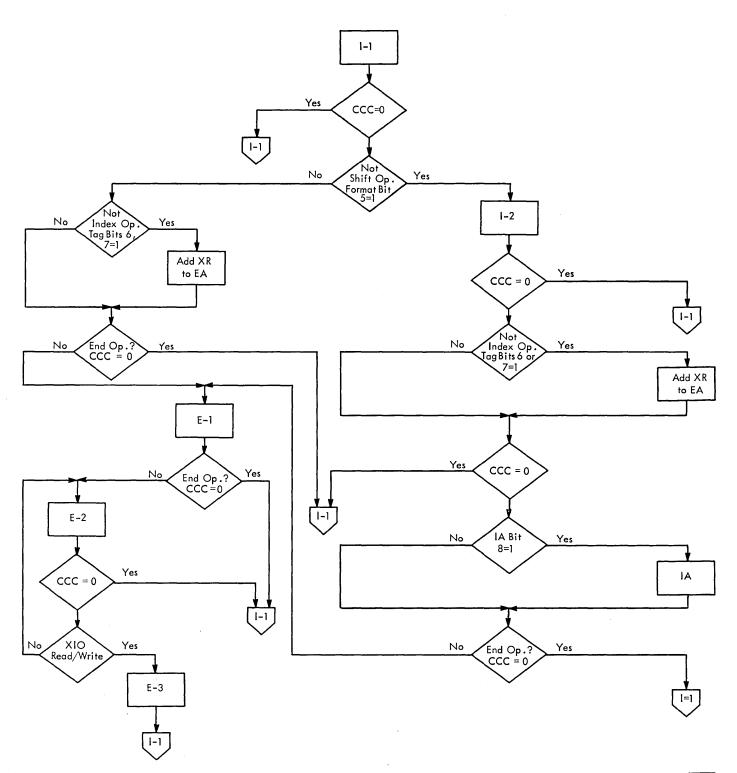

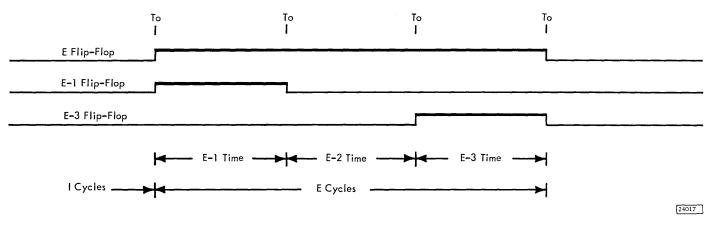

In the performance of the stored program instructions, the computer proceeds through instruction time (I-cycles), and generally execution time (Ecycles) for each operation (Figure 1-18). Instruction cycles read the instruction from core storage, store the instruction in control registers, and decode these control registers to specify a distinct operation.

The time required for the instruction cycles is dependent upon the type of instruction (Figure 1-19) and the factors to be used to develop the effective address.

All four I-cycles (I-1, I-2, I-X, and I-A) read and interpret instructions and develop an effective address (EA) for subsequent execute cycles.

Normal turn-on time and normal turn-off time of all I-cycle FF's is T0. A slight overlap of I-cycle FF's may occur at T0. This overlap will extend from the turn-on of one latch to the turn-off of the previous FF. For example, I-1 conditions the circuits required to turn on I-2. As I-2 is being turned on, I-1 is being turned off. An overlap of the two FF's may occur, depending upon the timing of the internal circuits of the FF.

Only functions common to all I-cycle FF's are performed during T0. The turn-on of successive FF's is interlocked by control gates to prevent more than one cycle (I-1, I-2, I-A, or I-X) FF from being on simultaneously during instruction time.

#### 1.13 INSTRUCTION CYCLE 1 (I-1)

- Used by all instructions.

- Stores the 16 bits of the first word of the instruction in control registers.

- Decodes the contents of the control registers to determine the operation to be performed.

- Reference Maintenance Diagram: AA 601.

This cycle reads the data from core storage at the address specified by the storage address register. (The instruction address register was set to the correct address during the previous instruction.) The core storage word is read into the B register, distributed from B register to the various control registers (Figure 1-20), and decoded to indicate the operation to be performed.

There are three major types of I-1 cycles:

- 1. I-1 used for single-word format instructions without indexing.

- 2. I-1 used for single-word format instructions with indexing.

- 3. I-1 used for all double-word format instructions.

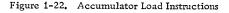

Figure 1-18. Program I Cycles - E Cycles

|                                                     | Сус | le R | equi | red |

|-----------------------------------------------------|-----|------|------|-----|

| Type Of Instruction                                 | 1-1 | 1-2  | IX   | IA  |

| Single - Word                                       | ×   |      |      |     |

| Single – Word With Indexing                         | ×   |      | ×    |     |

| Double - Word                                       | x   | x    |      |     |

| Double - Word with Indexing                         | x   | x    | ×    |     |

| Double - Word With Indirect Addressing              | x   | ×    |      | ×   |

| Double – Word With Indexing And Indirect Addressing | ×   | ×    | ×    | ×   |

|                                                     |     | ·    | 22   | 211 |

| B Register Bits               | Register                    |

|-------------------------------|-----------------------------|

| 0 to 4                        | Operation ( OP )            |

| 5                             | Format (Flag)               |

| 6 and 7                       | Index Address (Tag)         |

| 8 and 9                       | Modifier (Mod)              |

| 10 to 15                      | Cycle Control Counter (CCC) |

| 0 to 15                       | Data (D)                    |

| 14 and 15<br>by way of D reg. | Carry – Overflow (C/O)      |

|                               | 22                          |

Figure 1-19. Instruction Cycles

| Figure 1-20. | B Register to Control | Register Transfer |

|--------------|-----------------------|-------------------|

|--------------|-----------------------|-------------------|

Each type of I-1 cycle has a specific function in addition to the normal functions previously described.

# 1.13.1 Single-Word Format Without Indexing (F=0, Tag=00)

An effective address must be generated during this I-1 cycle that subsequently addresses the core storage word that is manipulated during the execute portion of the instruction.

The effective address is generated by loading the contents of I register into the accumulator and algebraically adding the displacement (bits 8 through 15 of the instruction) to the accumulator (I register contents).

**Circuit** Objectives

то:

- 1. Transfer I register to M register.

- 2. Increment I register.

# T1:

1. Transfer ACC to U register (save contents of ACC for future use).

# T2:

- 1. Read word at location specified by M register to B register.

- 2. Transfer B register bits 0-4 to operation register.

- 3. Transfer B register bit 5 to flag register (this bit must be off to specify single-word format).

- 4. Transfer B register bits 6 and 7 to tag register (these bits must be off to specify no indexing required).

- 5. Transfer B register bits 8 and 9 to MOD register.

- 6. Transfer B register bits 8-15 to D register bits 8-15 (second factor of effective address).

# Т3:

- 1. Set arithmetic control (required to add D register bits 8-15 to ACC).

- 2. Transfer I register to ACC (first factor of effective address).

# T4:

1. Add displacement (D register bits 8-15) to accumulator.

# <u>T5, T6:</u>

1. Continue add operation.

- T7:

- 1. Continue add operation (extend T7 if required).

- 2. Exit to E-1 cycle, or I-1 cycle as indicated by the operation code.

# $\frac{1.13.2 \text{ Single-Word Format With Indexing}}{(F=0, Tag \neq 00)}$

The effective address for this type of instruction is not generated completely during the I-1 cycle. However, the displacement portion of the instruction is placed in the accumulator so that the contents of the index register can be added to the displacement during the I-X cycle.

# **Circuit Objectives**

# <u>T0:</u>

- 1. Transfer I register to M register.

- 2. Increment I register

- T1:

- 1. Transfer ACC to U register (save contents of ACC for future use).

# T2:

- 1. Read word at the location specified by M register to B register.

- 2. Transfer B register bits 0-4 to operation register.

- 3. Transfer B register bit 5 to flag register (this must be off to specify single-word format).

- 4. Transfer B register bits 6 and 7 to tag register (one of these bits must be on to specify indexing).

- 5. Transfer B register bits 8 and 9 to MOD register.

- 6. Transfer B register bits 8-15 to D bits 8-15 (first factor of effective address).

# тз:

1. Set arithmetic control.

# T4:

1. Add displacement (D register bits 8-15) to accumulator.

T5, T6:

1. Continue add operation.

<u>T7:</u>

1. Exit to I-X Cycle.

# 1.13.3 Double-Word Format (F=1)

The effective address for this type of instruction is generated completely by I-cycles other than I-1. Therefore, this I-1 cycle does not set any factors into the accumulator other than the address of the address word.

**Circuit** Objectives

# <u>T0:</u>

- 1. Transfer I register to M register

- 2. Increment I register.

# <u>T1</u>:

1. Transfer ACC to U register (save contents of ACC for future use).

# T2:

- 1. Read word at location specified by M register to B register.

- 2. Transfer B register bits 0-4 to operation register.

- 3. Transfer B register bit 5 to flag register (this bit must be on to specify double-word format).

- 4. Transfer B register bits 6 and 7 to tag register.

- 5. Transfer B register bits 8 and 9 to MOD register.

T3:

1. Transfer I register +1 to the ACC, if Tag  $\neq 00$ .

# <u>T5:</u>

# <u>T7:</u>

1. Exit to I-2 cycle.

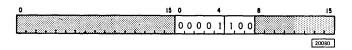

# 1.14 INSTRUCTION CYCLE 2 (I-2)

- Used by all double-word format instructions.

- Reads the 16 bits of the second word of the instruction into ACC via B register and D register. The second word in a double-word format instruction is the effective address unless it is modified by indexing or indirect addressing. In any event, the 16-bit address is placed in the accumulator during I-2. Any modification is made to the accumulator during IX or IA cycles.

- Reference Maintenance Diagram: AA601.

# **Circuit** Objectives

# то:

- Transfer I register to M register (I register was incremented by +1 during the previous I-1 cycle).

- 2. Increment I register.

# T2:

- 1. Read word at location specified by M register into B register.

- 2. Transfer B register to D register.

# T4:

1. Transfer D register to ACC.

# T7:

- 1. If either tag register FF is on (bit 6 or 7 of instruction);

- a. Set XR FF.

- b. Exit to I-X cycle.

- 2. If neither tag register FF is on, test MOD register for indirect addressing bit (Bit 8 of the instruction).

- a. If IA bit is on, set IA FF and exit to IA cycle.

- b. If IA bit is off, exit to E-1 cycle or I-1 cycle as indicated by the operation code.

# 1.15 INDEXING CYCLE (I-X)

• Reads the contents of the index register addressed by the tag bits of the instruction (bits 6 and 7).

<sup>1.</sup> Set CCC to 1.

- Generates an effective address (add XR to contents of accumulator) for the data to be manipulated during the following execute time.

- Indexing takes precedence over indirect addressing.

- Instruction address is not changed.

- Arithmetic check indicators are not altered.

- Reference Maintenance Diagram: AA601.

The I-X cycle reads the contents of the index register specified by the tag bits of the instruction (bits 6 and 7 now in the tag register) and adds the contents of the XR to the contents of the accumulator (displacement if single-word format; address word if double-word format).

The contents of the accumulator is always considered as positive (absolute). The instruction as it appears in core storage is not changed by the indexing operation.

When an address is indexed and indirect, the indexing procedure has precedence. The resulting effective address after indexing is the new effective indirect address. The address at the indirect address must be a direct address (only one indexing and one indirect addressing operation are allowed for each instruction).

The three index registers are located in the first three core storage locations (addresses 0001, 0002, and 0003). The index registers are addressed by circuits which block the normal output of the M register and decode the contents of tag register to energize the M register output lines for bits 14 and 15.

### Circuit Objectives

T7 of previous I-1 or I-2 cycle.

1. Set XR address FF (this FF blocks the normal M register output).

# T0 of I-X cycle.

1. Select index register by raising correct M register bit 14 and/or bit 15 output.

<u>T1:</u>

1. Note that the I-X cycle does not transfer ACC to the U register. This is because U register contains the accumulator data developed

during a previous instruction and the accumulator contains the address that must be indexed.

### T2:

- 1. Read word at location specified by M register to B register.

- 2. Transfer B register to D register.

<u>T 3:</u>

1. Set arithmetic control.

<u>T4</u>:

- 1. Algebraically add D register (contents of index register) to ACC (effective address).

- Т5, Т6:

- 1. Continue add operation.

- <u>T7:</u>

- 1. Continue add operation, if required.

- 2. Extend T7 cycle if required.

- 3. Exit to I-A cycle if Modifier bit 8 is on.

- 4. Exit to I-1 or E-1 as indicated by operation code, if IA bit is off.

- 1.16 INDIRECT ADDRESSING CYCLE (I-A)

- Reads a direct address from the core storage location specified by the indirect address in the accumulator.

- Transfers the direct address to the accumulator to replace the indirect address.

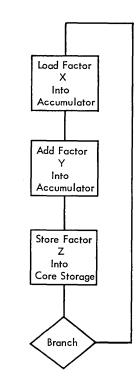

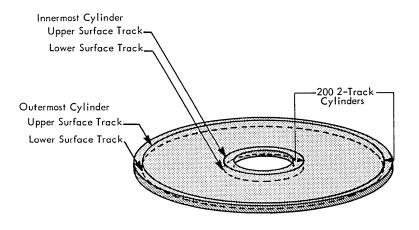

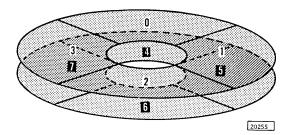

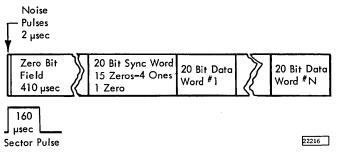

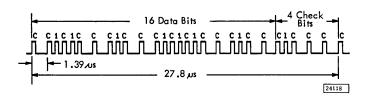

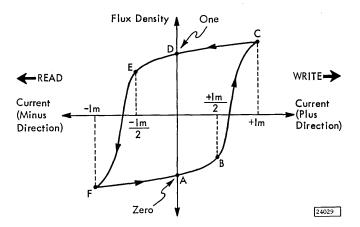

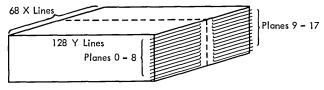

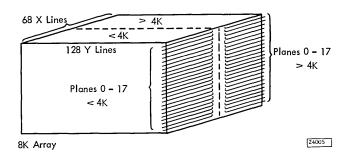

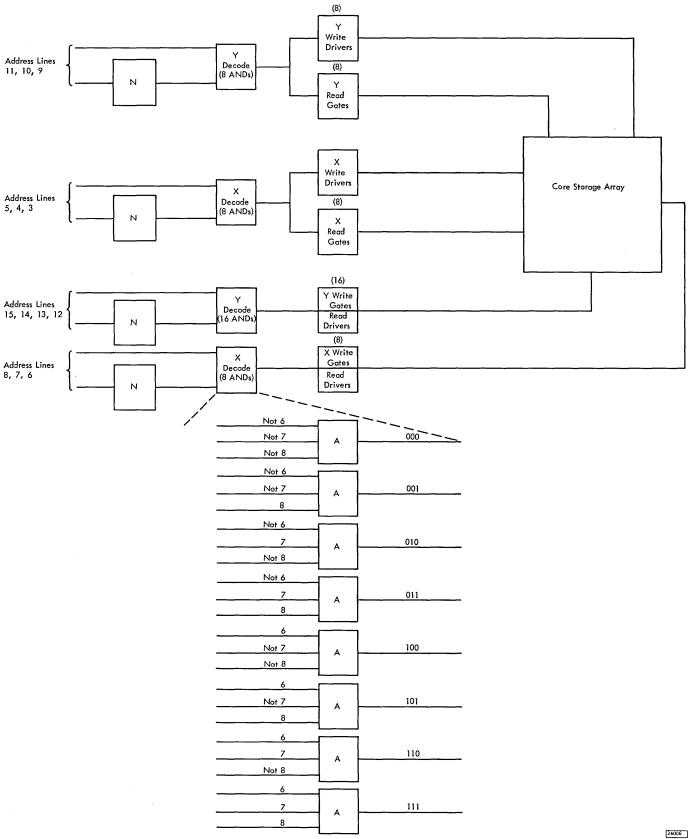

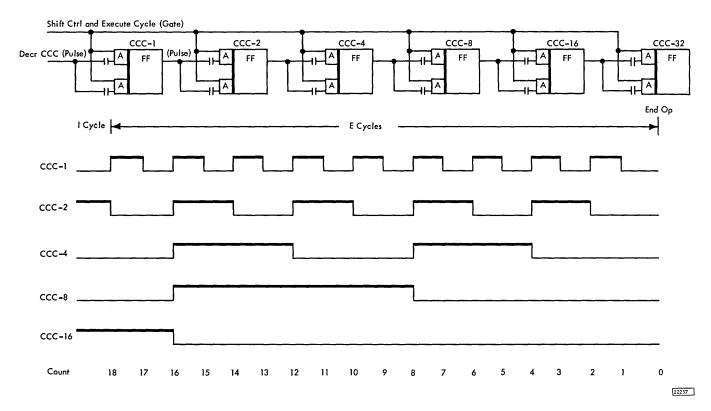

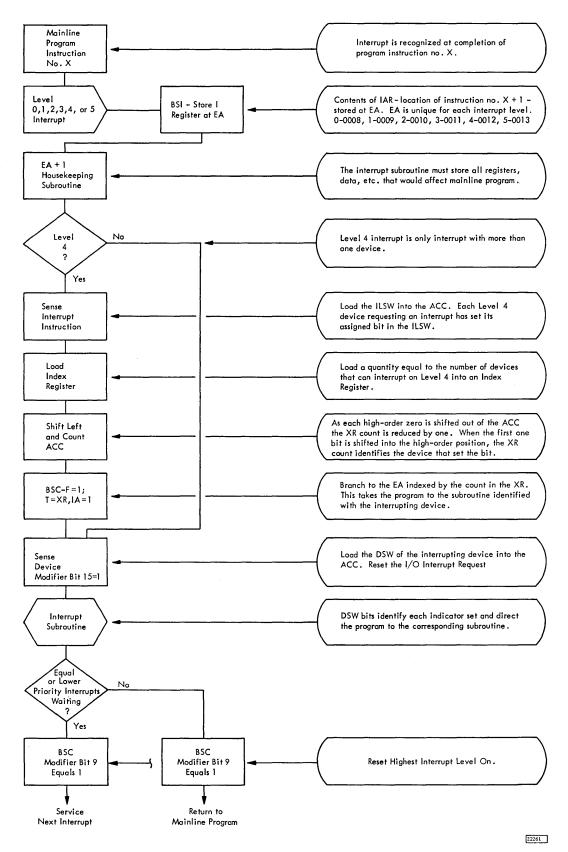

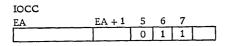

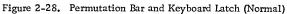

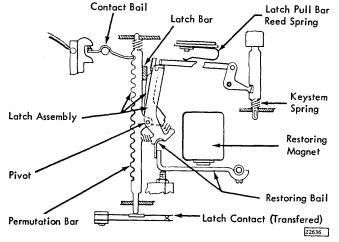

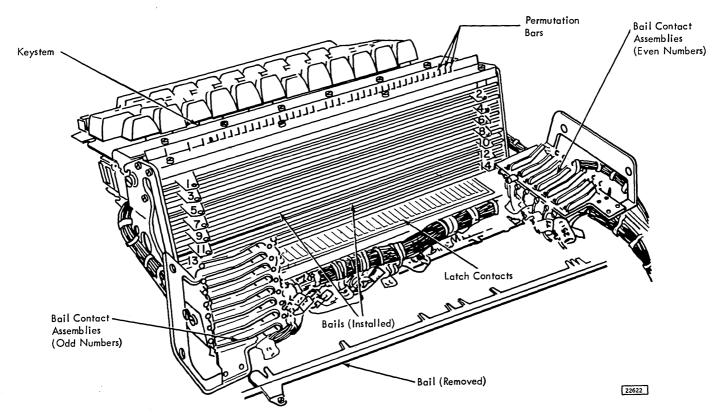

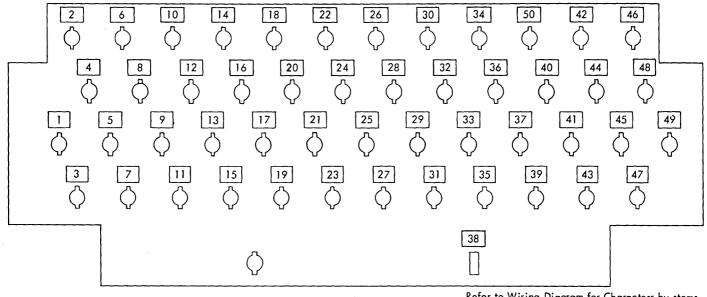

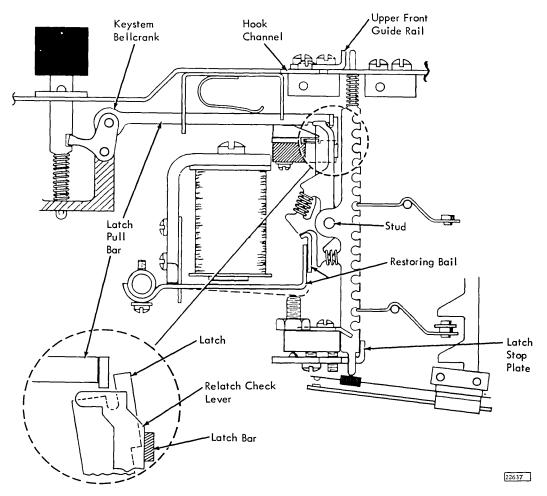

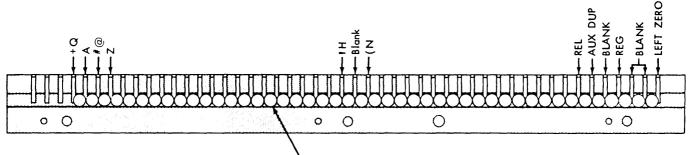

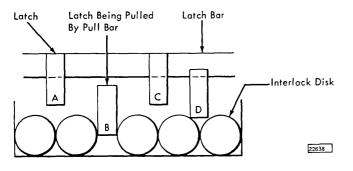

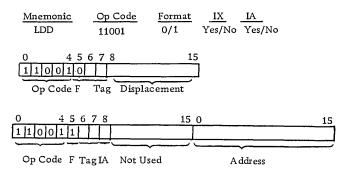

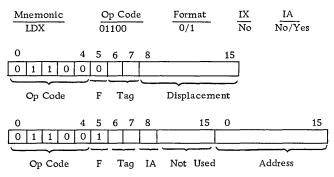

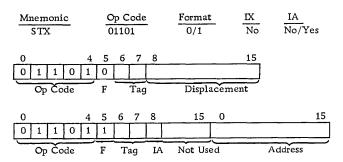

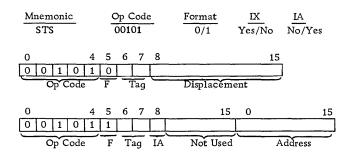

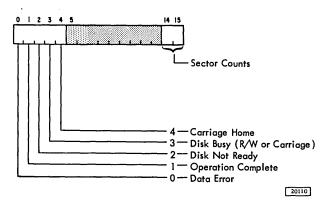

- Reference Maintenance Diagram: AA601.