Field Engineering

Theory-Maintenance

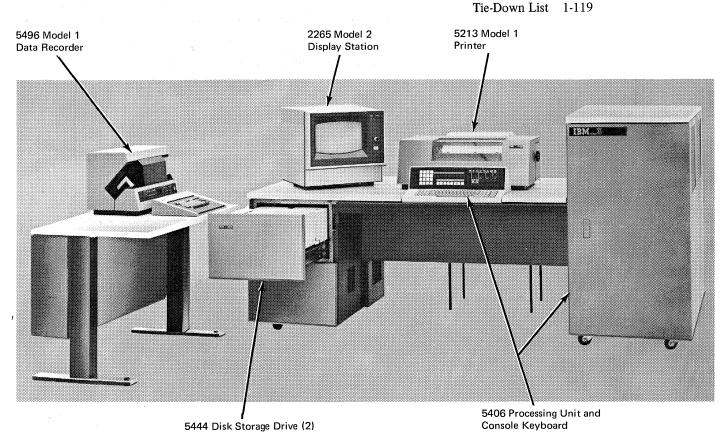

System/3 Model 6 5406 Processing Unit and Attachments

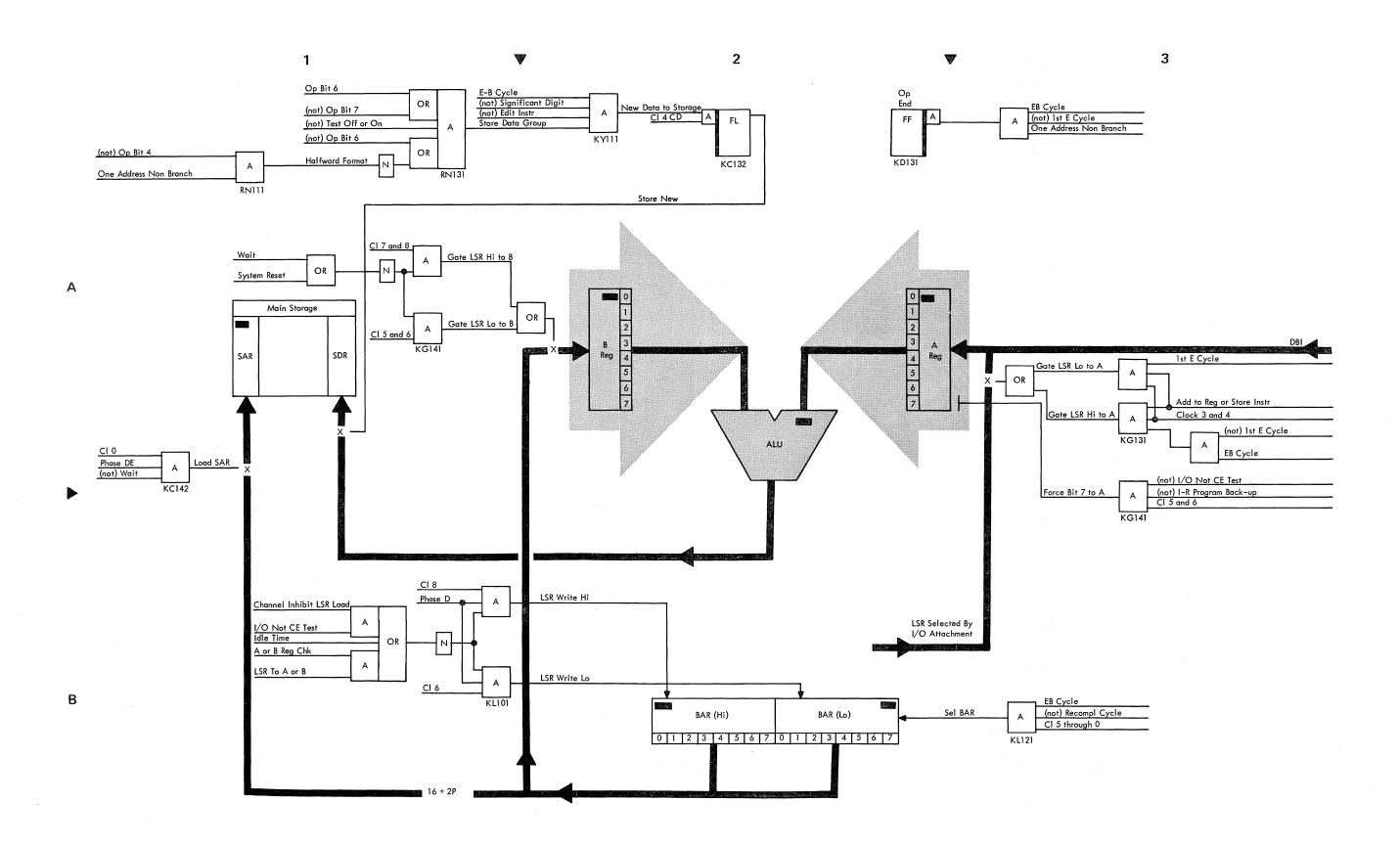

# Preface

**Abbreviations**

XR

This manual is a combined theory-diagram and maintenance manual for the 5406 Processing Unit. It is divided into eleven sections, and with the following exceptions it is a self-contained manual:

TNL SN34-0043 to SY34-0022-1

- 1. Sections 2 through 6 are the diagrams for the processing unit, and must be used in conjunction with the Field Engineering Theory of Operations Manual, *IBM System/3 Model 6 5406 Processing Unit*, Order No. SY34-0023.

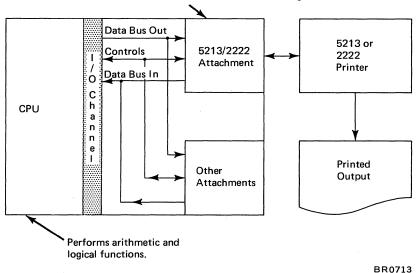

- 2. Section 8 is the disk file attachment manual which is a separate theory-diagram manual. The Field Engineering Theory-Diagrams Manual (*IBM System/3 5444 Disk Storage Drive Attachment*, Order No. SY34-0021) can be inserted, in sequence, in this manual.

- 3. The binary synchronous communications adapter (BSCA) and serial input output channel (SIOC) feature attachment manuals are separate theory-diagrams manuals which are also required if these features are present on the system.

The eleven sections of the manual are as follows:

| Section | Title                                      |

|---------|--------------------------------------------|

| 1       | System Maintenance                         |

| 2       | Error Conditions                           |

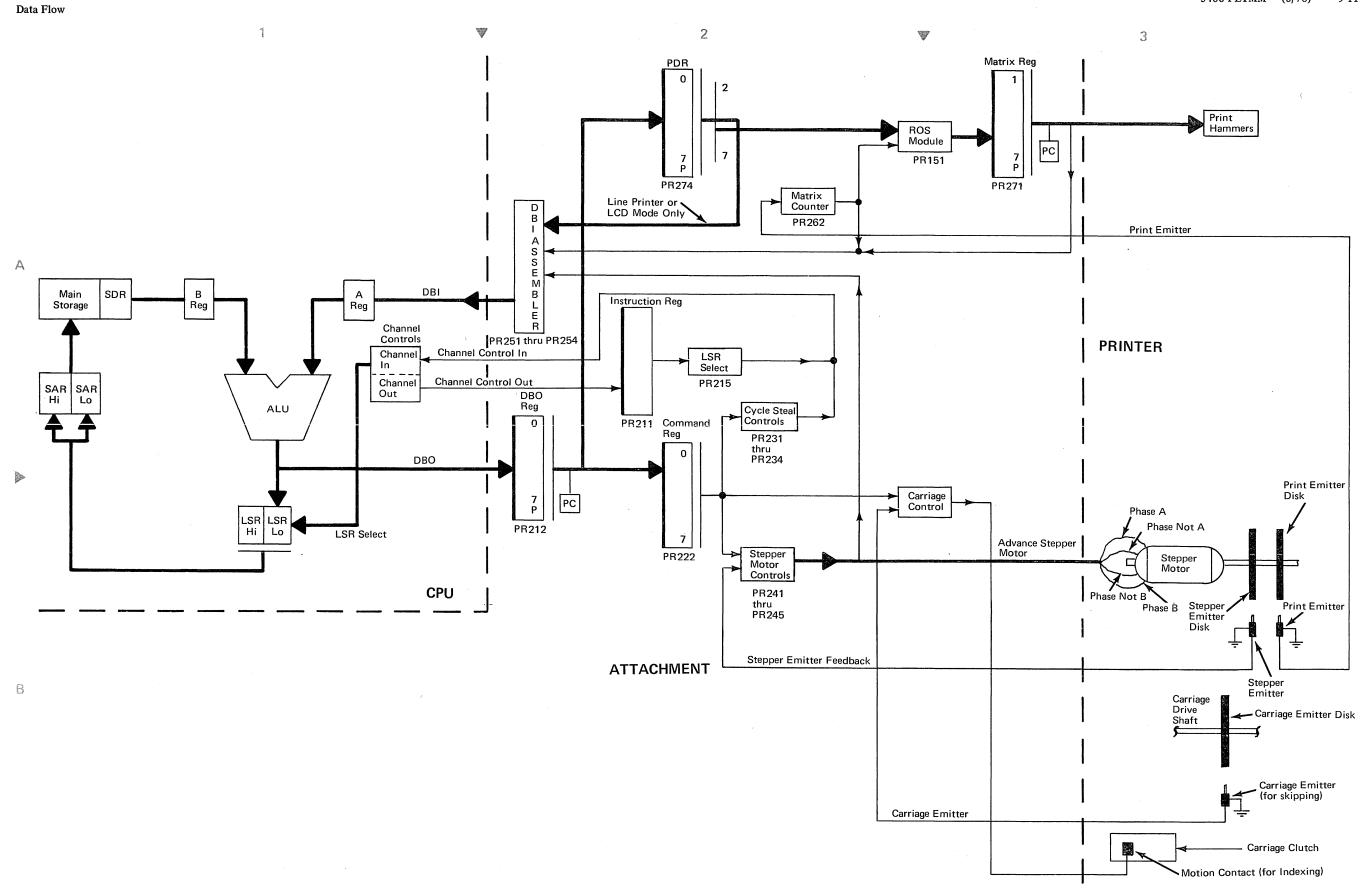

| 3       | Data Flow                                  |

| 4       | Functional Units CPU Sections              |

| 5       | Operations                                 |

| 6       | Power and Cooling                          |

| 7       | Keyboard and Console                       |

| 8       | Disk File Attachment (separate manual)     |

| 9       | Printer and Ledger Card Device Attachments |

| 10      | Data Recorder Attachments                  |

| 11      | CRT Attachment                             |

|         |                                            |

Other manuals necessary to understand and service the IBM System/3 Model 6 are:

- 1. Field Engineering Parts Catalog, *IBM 5406 Processing Unit*, Order No. S134-0001

- 2. Field Engineering Maintenance Diagrams, *IBM System/3 Serial I/O Channel Attachment*, Order No. SY31-0275

- 3. Field Engineering Maintenance Diagrams, *IBM System/3 Binary Synchronous Communications Adapter*, Order No. SY31-0258

- 4. Field Engineering Theory-Maintenance Diagrams, *IBM 5496 Data Recorder Online Feature*, Order No. SY31-0279

- 5. Field Engineering Theory-Maintenance Manual, *Elastic Diaphragm Encoded Keyboards*, Order No. SY27-0073

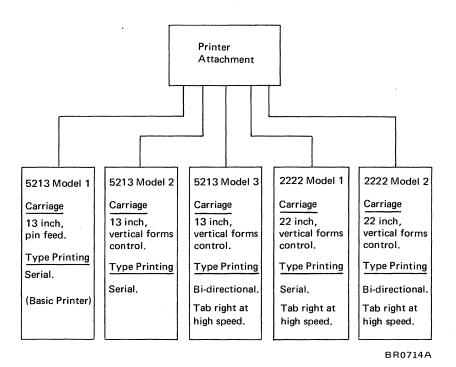

- 6. Maintenance Library Theory-Maintenance Manual, *IBM 2222 Printer Models 1 and 2*, Order No. SY24-3585

# Second Edition (February 1971)

This is a revision of, and obsoletes SY34-0022-0. Changes and corrections were made to -all chapters and sections. The basic content and format remain the same.

Within this manual, System/3 machines made for use in the United States are referred to as domestic machines, machines made for use in countries other than the United States are referred to as World Trade machines.

Changes to the information in this manual will be reported in subsequent revisions or supplements.

Copies of this and other IBM publications can be obtained through IBM Branch Offices.

A form for readers' comments is provided at the back of this publication. If the form has been removed, send your comments to IBM Corporation, General System Division, Systems Publications, Department 707, Boca Raton, Florida 33432.

©Copyright International Business Machines Corporation 1970, 1971

|   | AAR    | A field Address Register                       |

|---|--------|------------------------------------------------|

|   | ALD    | Automated Logic Diagram                        |

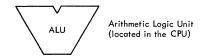

|   | ALU    | Arithmetic Logic Unit                          |

|   | ARR    | Address Recall Register                        |

|   | BAR    | B field Address Register                       |

|   | BSCA   | Binary Synchronous Communications Adapter      |

|   | BSM    | Basic Storage Module                           |

|   | CPU    | Central Processing Unit                        |

|   | CR     | Condition Register                             |

|   | CRR    | Condition Recall Register                      |

|   | CRTAR  | CRT Address Register                           |

|   | DA     | Device Address                                 |

|   | DBI    | Data Bus In                                    |

|   | DBO    | Data Bus Out                                   |

|   | DFCR   | Disk File Control Register                     |

|   | DFDR   | Disk File Data Register                        |

|   | DPF    | Dual Program Feature (not used on the 5406)    |

|   | DRAR   | Data Recorder Address Register                 |

|   | DRR    | Data Recall Register                           |

|   | EBCDIC | Extended Binary Coded Decimal Interchange Code |

|   | IAR    | Instruction Address Register                   |

|   | I/O    | Input—Output                                   |

|   | K      | Thousand                                       |

| 1 | LCD    | Ledger Card Device                             |

| • | LCR    | Length Count Register                          |

|   | LCRR   | Length Count Recall Register                   |

| 1 | LLAR   | Locate Line Address Register                   |

| ٠ | LSR    | Local Storage Register                         |

|   | MAP    | Maintenance Analysis Procedure                 |

|   | MST    | Monolithic System Technology                   |

|   | PC     | Parity Check                                   |

|   | PCAR   | Print Command Address Register                 |

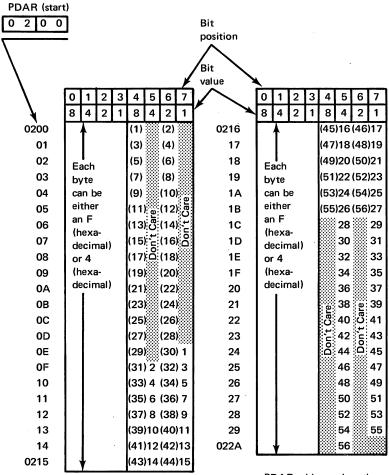

|   | PDAR   | Print Data Address Register                    |

|   | PG     | Parity Generate                                |

|   | POR    | Power On Reset                                 |

|   | PSR    | Program Status Register                        |

|   | SAR    | Storage Address Register                       |

|   | SDR    | Storage Data Register                          |

|   | SIOC   | Serial Input Output Channel                    |

|   | ND.    | T. 1. D.                                       |

Index Register

5406 FETMM (6/71)

# Contents

| Section 1. | System Maintenance                           |      |       |

|------------|----------------------------------------------|------|-------|

| Chapter 1. | Reference Data                               |      | 1-101 |

| Chapter 2. | Console and Maintenance Facilities           |      | 1-201 |

| Chapter 3. | Preventive Maintenance                       |      | 1-301 |

| Chapter 4. | Checks, Removals, and Adjustment             |      | 1-401 |

| Chapter 5. | Power and Cooling                            |      | 1-501 |

| Chapter 6. | Locations                                    |      | 1-601 |

| Section 2. | Processing Unit                              |      |       |

| Error Cond | ditions                                      |      | 2-010 |

| Section 3. | Processing Unit                              |      |       |

|            | · · · · · · · · · · · · · · · · · · ·        |      | 3-010 |

| Data i low |                                              | •    | 00.0  |

| Section 4. | Processing Unit                              |      |       |

| Functional | Units                                        | •    | 4-010 |

| Costion E  | Processing Unit                              |      |       |

|            |                                              |      |       |

| Operations |                                              | •    | 5-005 |

| Section 6. | Processing Unit                              |      |       |

| Power and  | Cooling                                      |      | 6-010 |

|            |                                              |      |       |

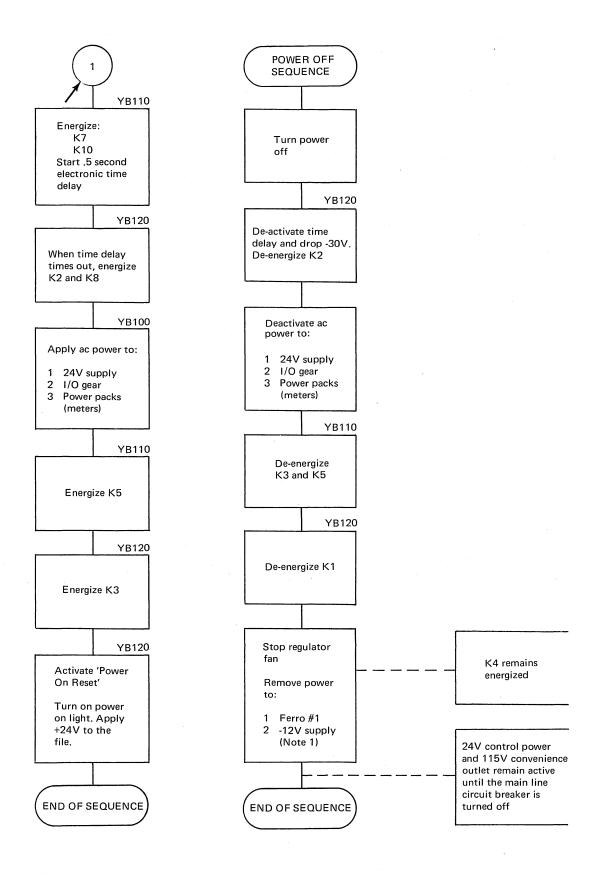

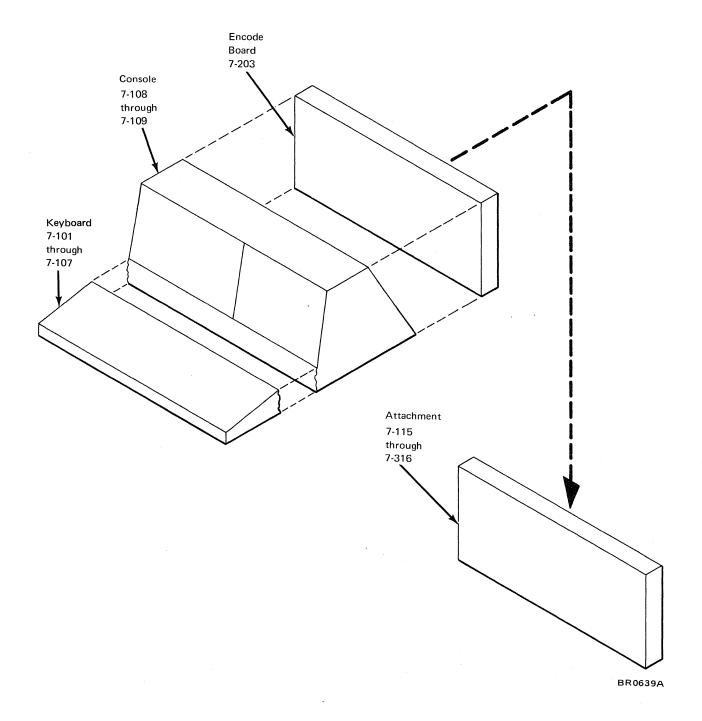

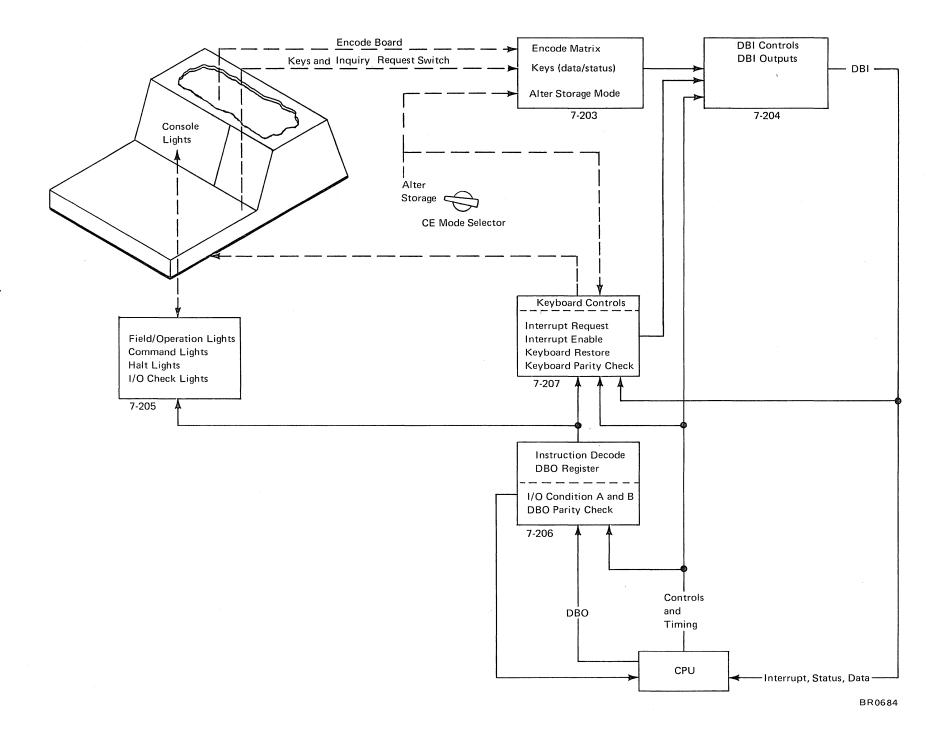

| Section 7. | Keyboard and Console                         |      |       |

| Chapter 1. | Introduction                                 |      | 7-101 |

|            | Functional Units                             |      | 7-201 |

|            | Operations                                   |      | 7-301 |

| •          | •                                            |      |       |

| Section 8. | Disk Storage Drive Attachment (separate manu | ıal) |       |

| Chapter 1. | Introduction                                 |      | 8-101 |

| Chapter 2. | Functional Units                             |      | 8-201 |

| Chapter 3. | Operations                                   | •    | 8-301 |

| Section 9. | Printer and Ledger Card Device Attachments   |      |       |

|            |                                              |      | 0.101 |

|            | Printer Attachment Introduction              | •    |       |

| -          | Printer Attachment Functional Units          | •    | 9-201 |

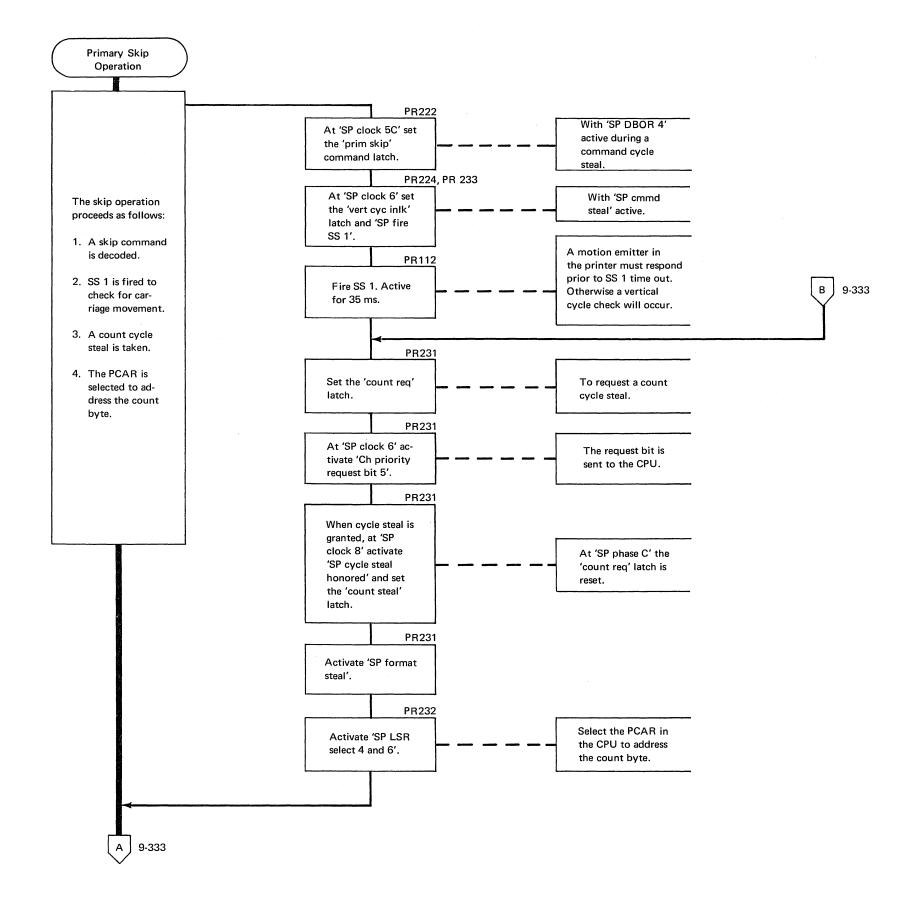

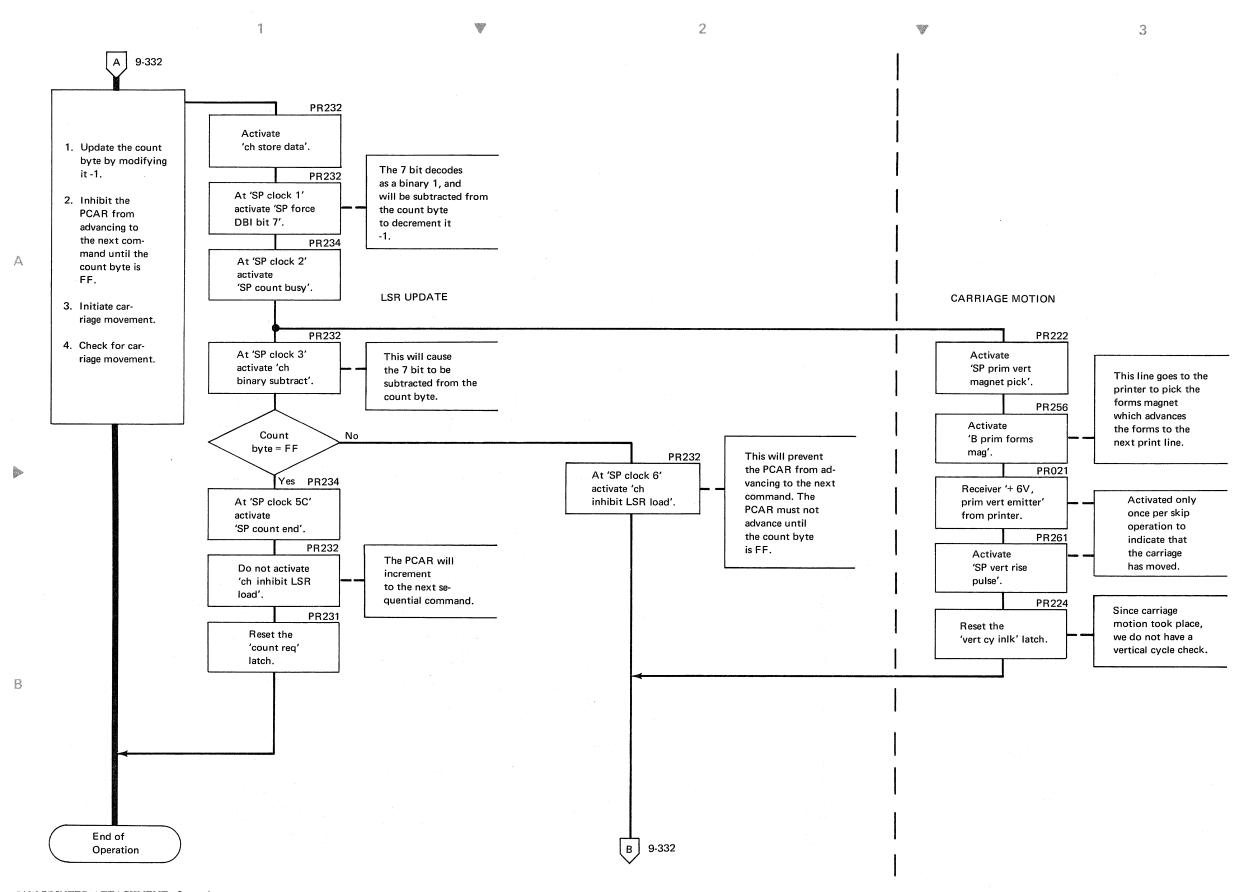

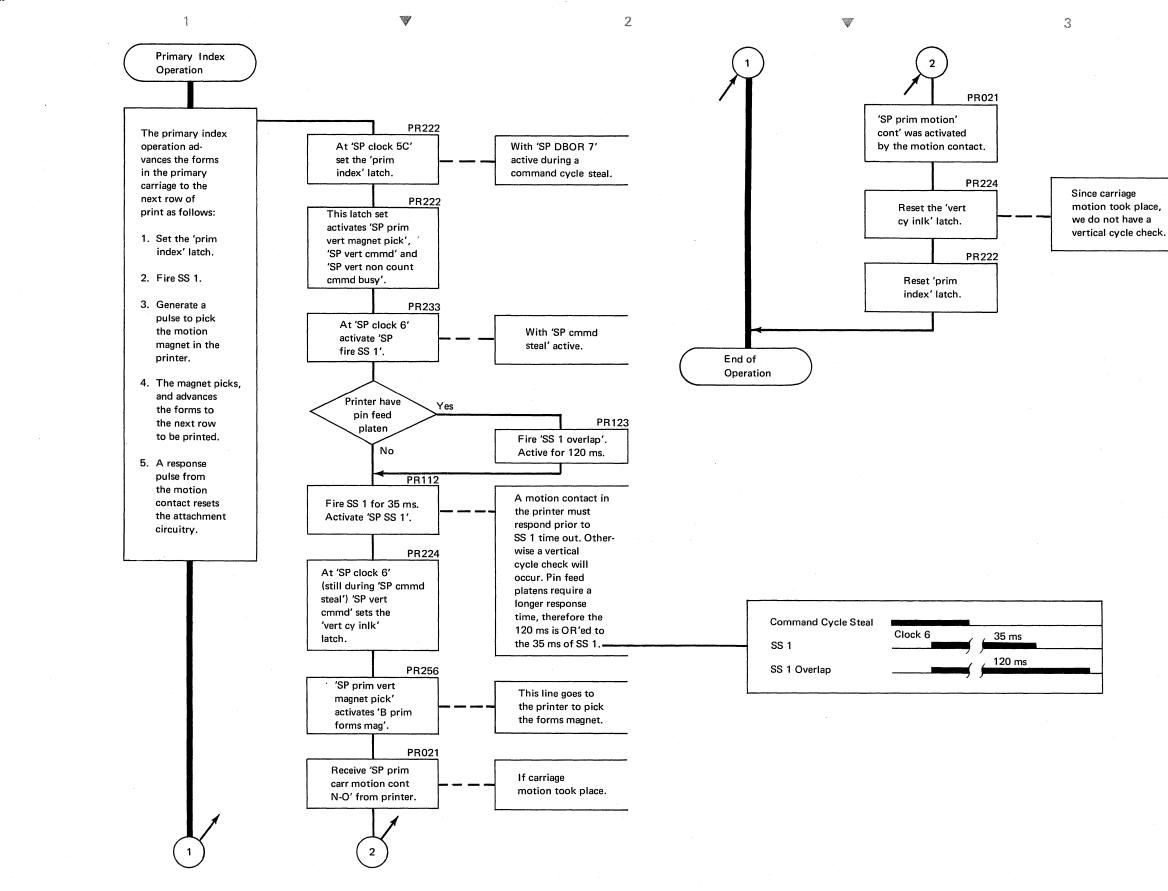

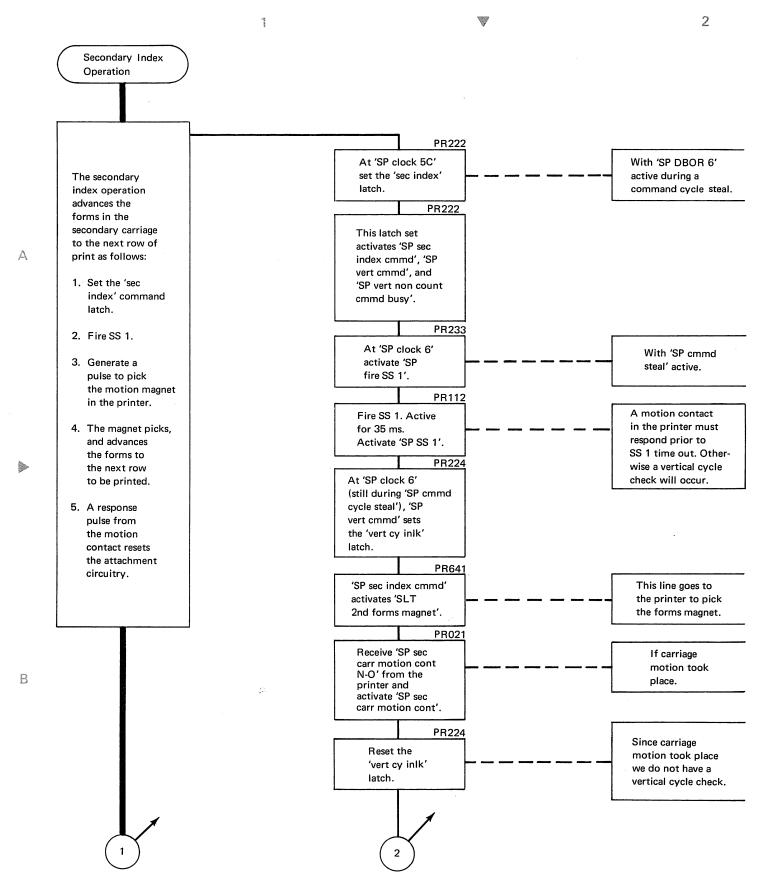

| •          | Printer Attachment Operations                | •    | 9-301 |

|            | Ledger Card Device Attachment Introduction   | ٠    | 9-401 |

|            | Ledger Card Device Attachment Functional     |      | 0.504 |

|            | Ledger Card Device Attachment Operations     |      |       |

| nantar 6   | Legger Card Device Attachment (Ingrations    |      | น.ผกา |

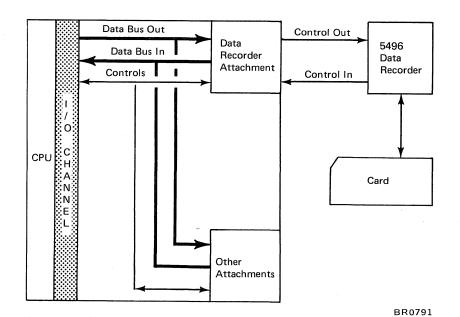

| Section 10. | . Data Recorder A       | ۱tta | ich | me | nt |  |  |  |       |

|-------------|-------------------------|------|-----|----|----|--|--|--|-------|

| Chapter 1.  | Introduction .          |      |     |    |    |  |  |  | 10-10 |

| Chapter 2.  | Functional Units        |      |     |    |    |  |  |  | 10-20 |

| Chapter 3.  | Operations              |      |     |    |    |  |  |  | 10-30 |

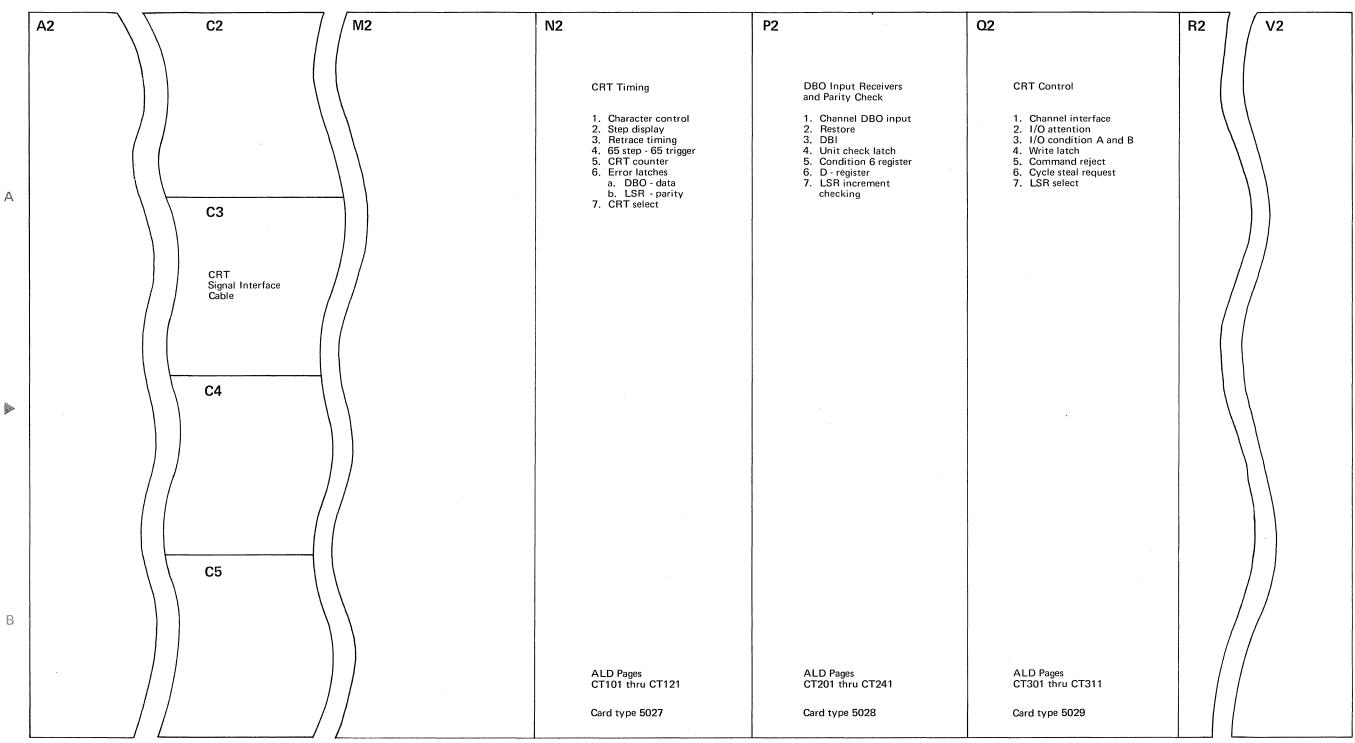

| Section 11. | . CRT Attachmen         | t    |     |    |    |  |  |  |       |

| Chapter 1.  | Introduction .          |      |     |    |    |  |  |  | 11-10 |

| Chapter 2.  | <b>Functional Units</b> |      |     |    |    |  |  |  | 11-20 |

| Chapter 3.  | Operations              |      |     |    |    |  |  |  | 11-30 |

|             |                         |      |     |    |    |  |  |  |       |

TNL SN34-0043 to SY34-0022-1 5406 FETMM (6/71) iii

Register Reset

Boolean Algebra Symbols

- In a line name means "And"

- + In a line name means "Or"

(xx - - - x) Indicates a line name that does not exist as an actual ALD name, but used to better explain the function of a line or block

\* Indicates a point that can be scoped on back-panel pins.

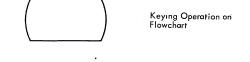

Decision Block on a Flowchart (Asks a question)

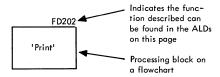

Single quotes in the block indicate a line name, flip latch, or flip flop name

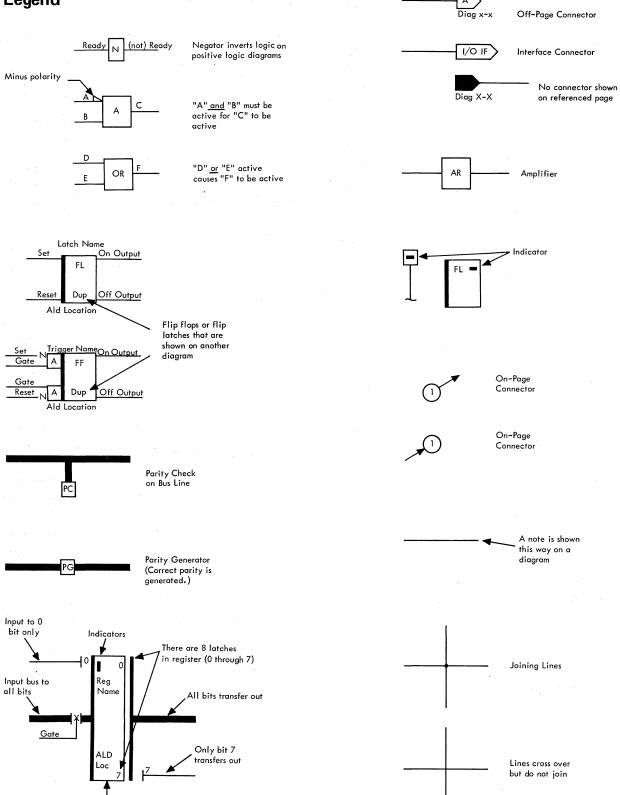

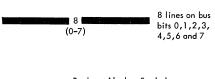

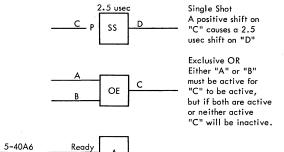

# Legend

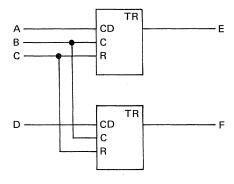

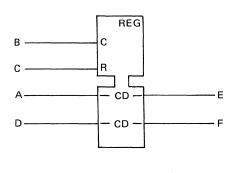

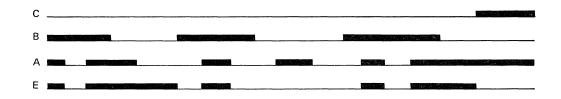

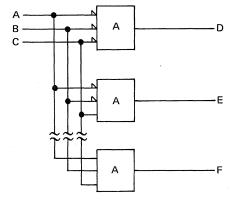

# REGISTER (REG)

- A register is a functional logic block consisting of a group of associated triggers (TR) with common lines such as reset (R), control (C), etc. Common gates may also be included.

- Common Section.

Contains lines common to one or more logic elements.

Data Section

The inputs and/or outputs shall be grouped and shall be interconnected with lines and connecting symbol.

Name

The common section shall have the name "REG".

## Examples:

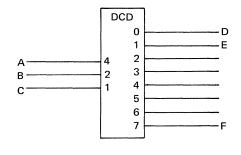

# DECODER (DCD)

- A functional logic block in which inputs and outputs are assigned numeric values.

An output line is active when and only when its value (number) is equal to the sum of the values of all active input lines.

- Note: At any given time there is only one sum. If all input lines are inactive, the sum is zero.

- Common Section.

When gating is used, the gating line and gated line shall be cross-related by labeling with a letter, rather than a numeral. These common lines shall be drawn to the common section. The common section is not used if there are no common lines.

Data Section.

The inputs to a decode block shall be number 1, 2, 4, 8, 16, etc. The outputs shall be numbered to reflect the sum of the active inputs required for each decode output.

Name

The common section (when used) shall have the name "DCD"; when the common section is not used, the data section shall have the name "DCD".

Example 1: Decoder without gating.

| <b>.</b> |

|----------|

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

# Section 1. System Maintenance

#### Contents

This section of the combined theory-maintenance manual (FETMM) contains the maintenance procedures for the 5406. It is divided into six chapters as follows:

Chapter 1. Reference Data

Chapter 2. Console and Maintenance Facilities

Chapter 3. Preventive Maintenance

Chapter 4. Checks, Adjustments, and Removals

Chapter 5. Power and Cooling

Chapter 6. Locations

## Chapter 1. Reference Data 1-101

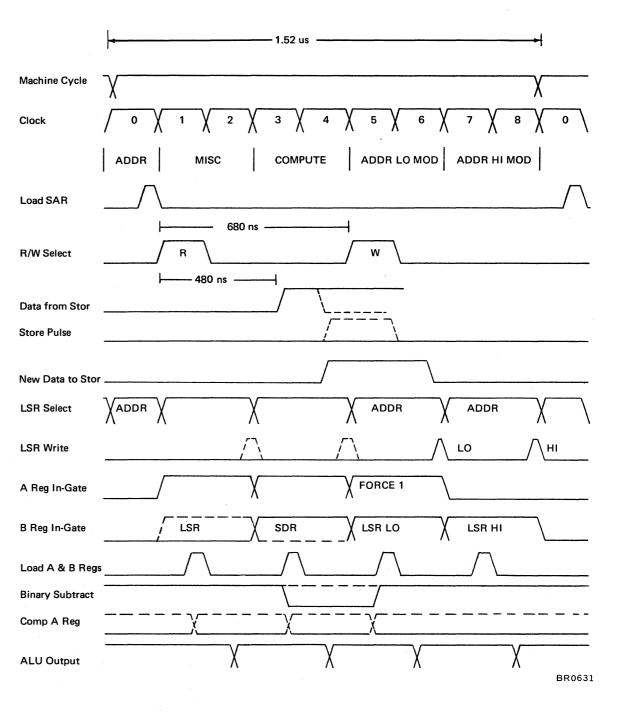

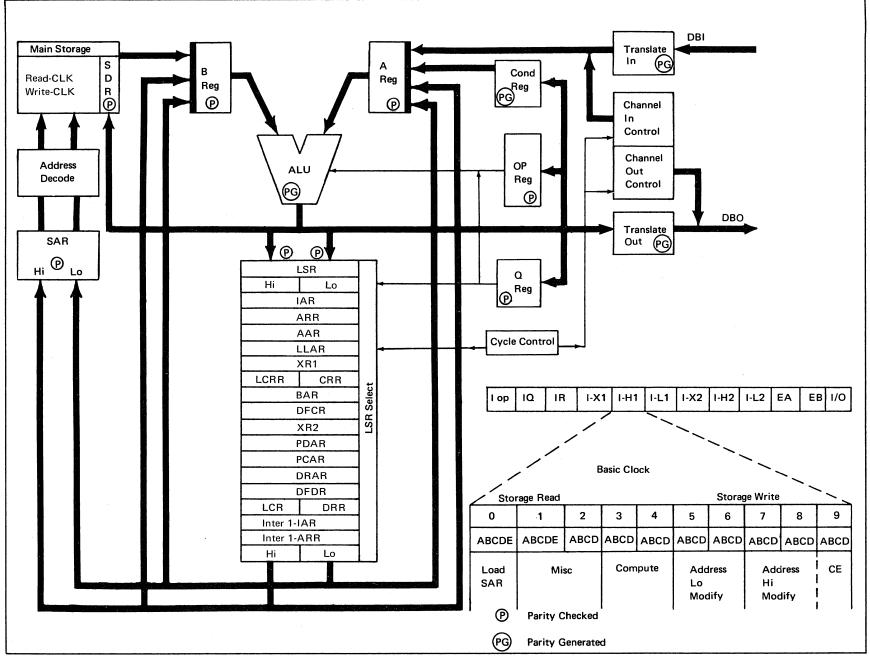

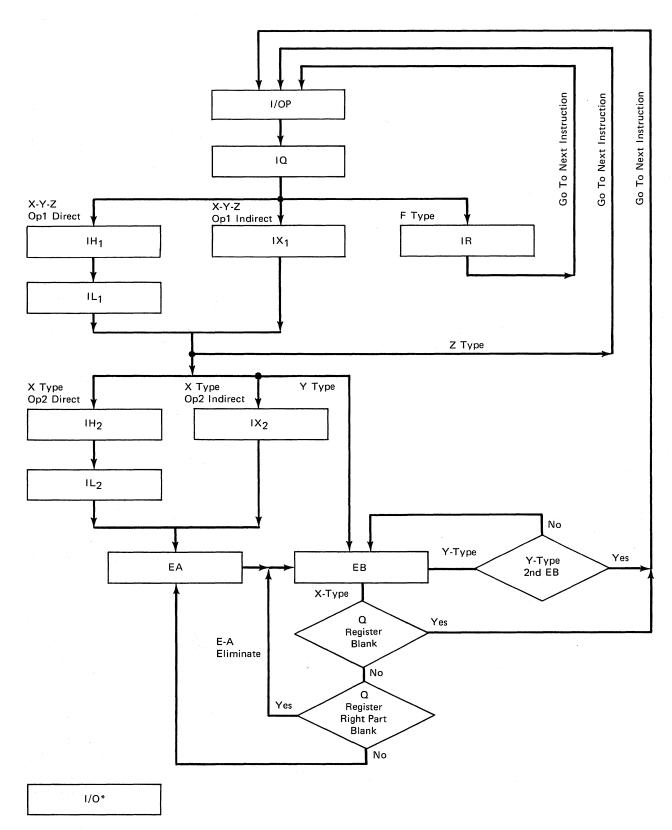

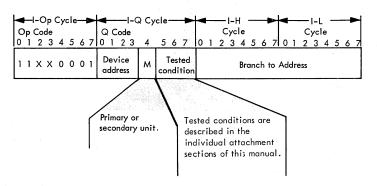

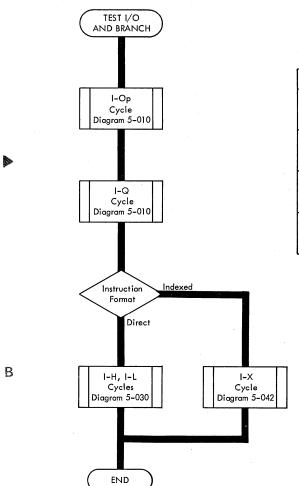

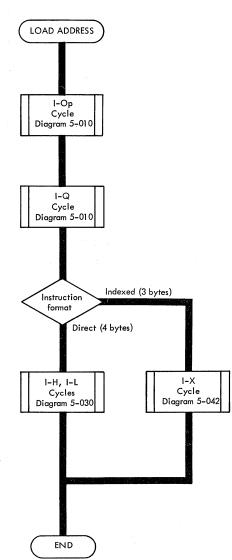

Instructions 1-101 Instruction Codes and Addressing Schemes 1-102 Instruction and Machine Cycles 1-103 Test I/O and Branch Instruction 1-104 Load I/O Instruction 1-105 Start I/O Operation 1-106 Sense Instruction (3 Parts) 1-107 through 1-109 I/O Control Fields 1-110 CPU Sense and Condition Code Response 1-111 Condition Register Settings and Hexadecimal and Decimal Conversion Chart 1-112 Hexadecimal Addition and CPU Timing 1-113 Local Store Registers and Data Flow 1-114 Cycle Pattern, Data Storage and Sign Control 1-115 Code Conversion Chart (2 Parts) 1-116, 1-117 CRT Code Conversion Chart 1-118

BR0435

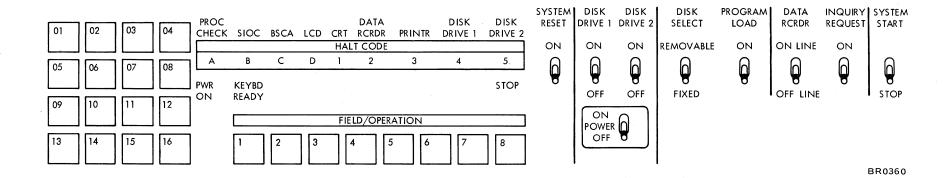

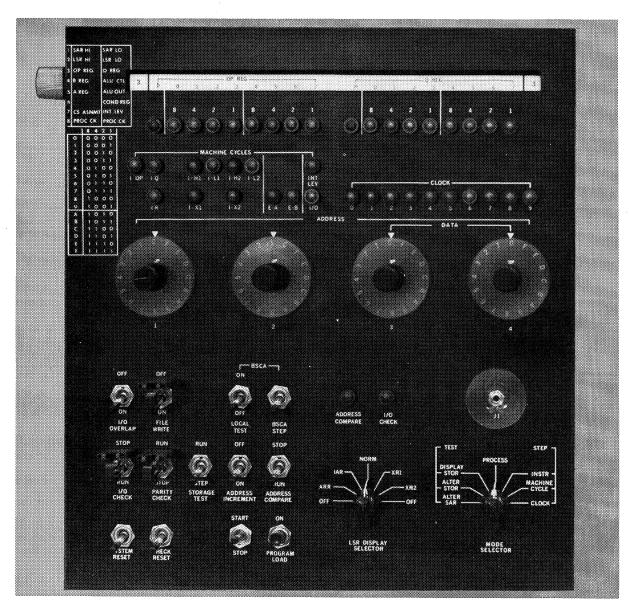

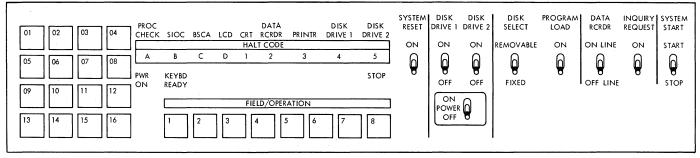

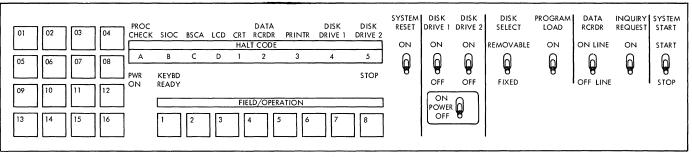

## Chapter 2. Console and Maintenance Facilities 1-201

Integrated Maintenance Package 1-201

System Console (2 Parts) 1-202, 1-203

Field Engineer Console (4 Parts) 1-204 through 1-207

Special Tools (2 Parts) 1-208, 1-209

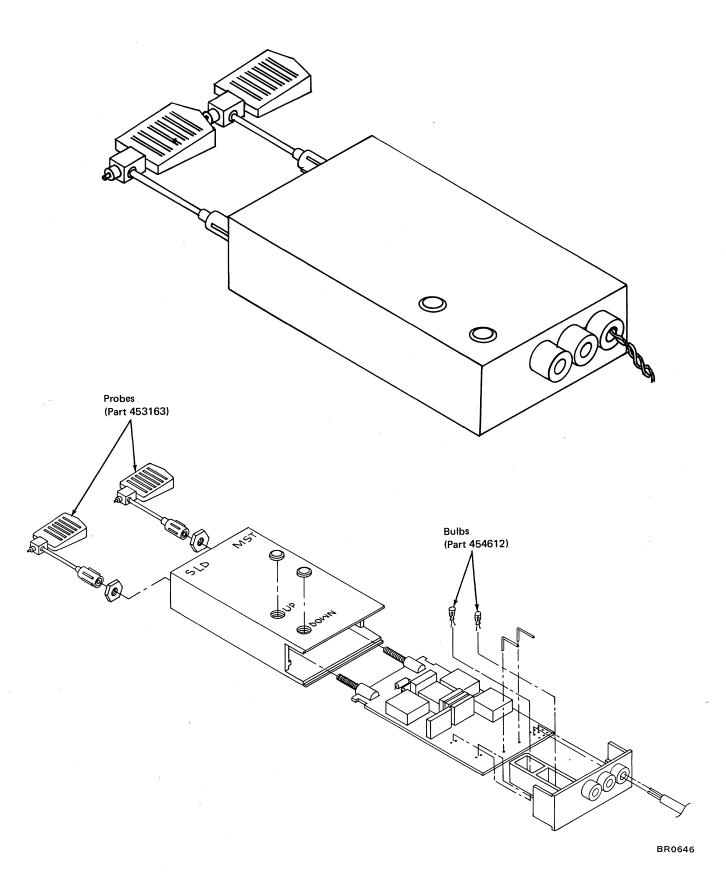

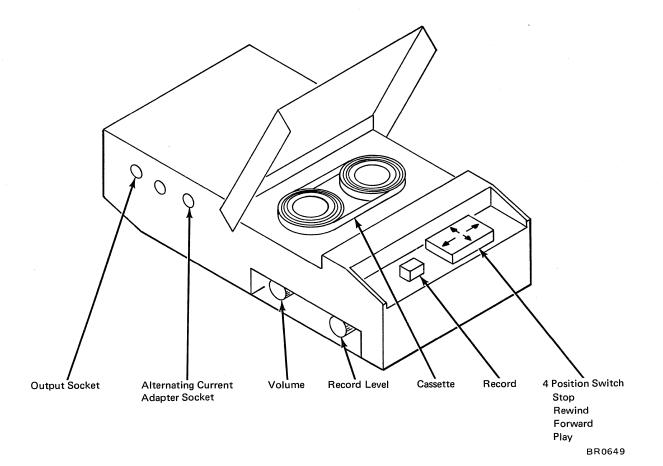

Alternate Program Load Device (2 Parts) 1-210, 1-211

## Chapter 3. Preventive Maintenance 1-301

Preventive Maintenance Chart 1-301

## Chapter 4. Checks, Adjustments, and Removals 1-401

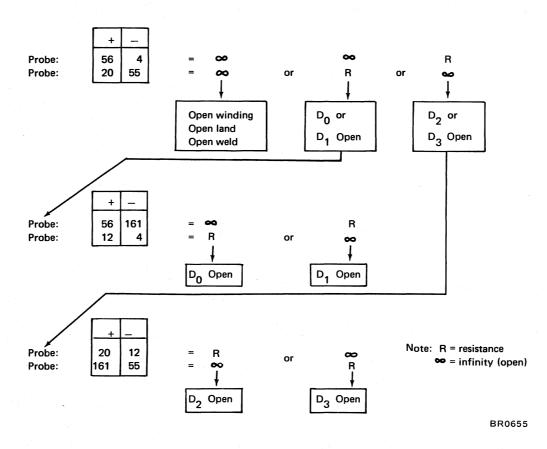

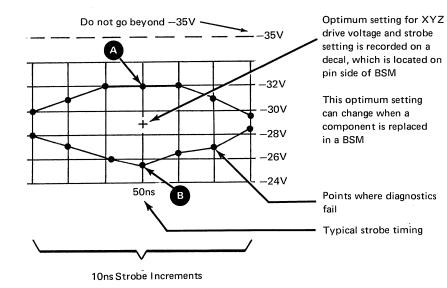

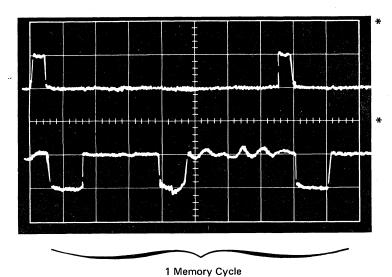

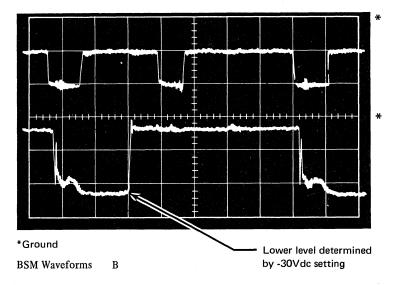

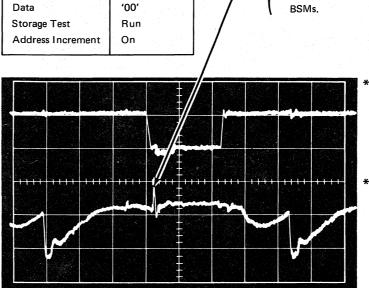

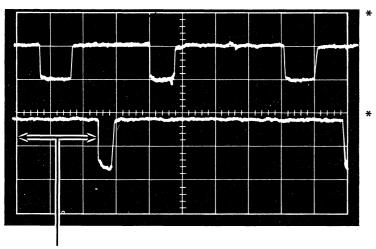

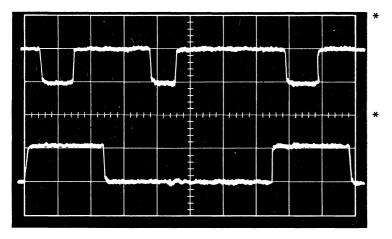

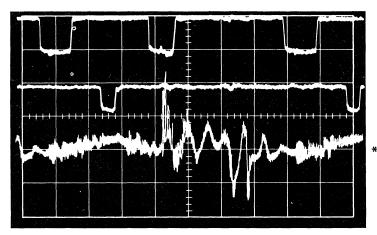

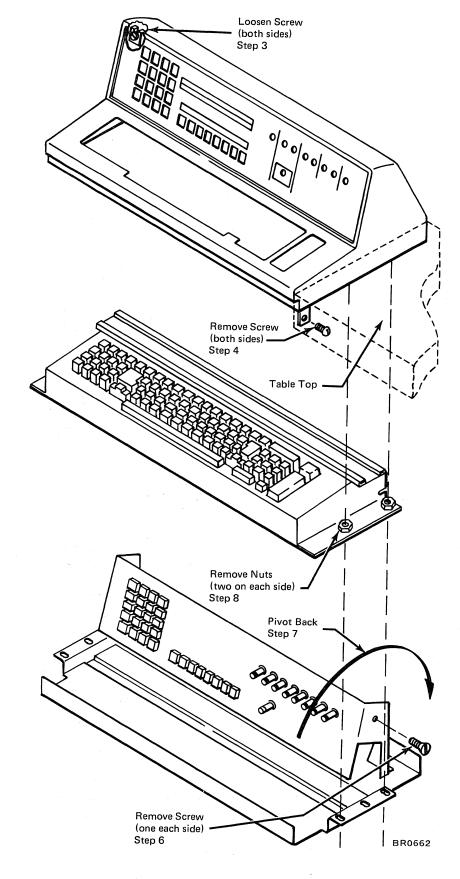

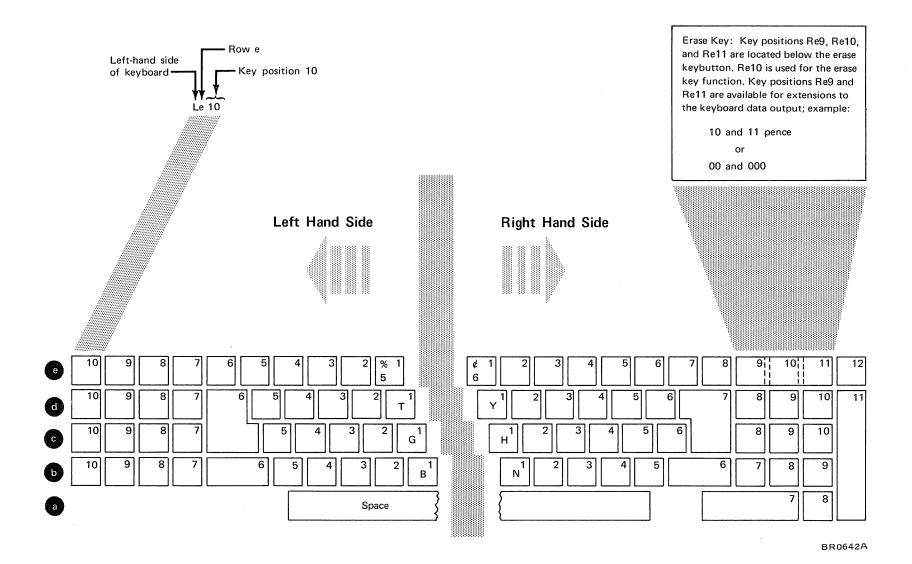

Storage Module (11 Parts) 1-401 through 1-408C Keyboard 1-409 Single Shots 1-410 5444 Disk 1-411 5496 Data Recorder 1-412

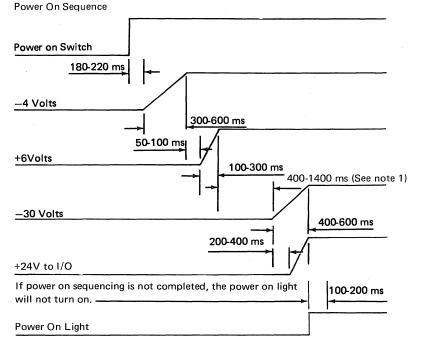

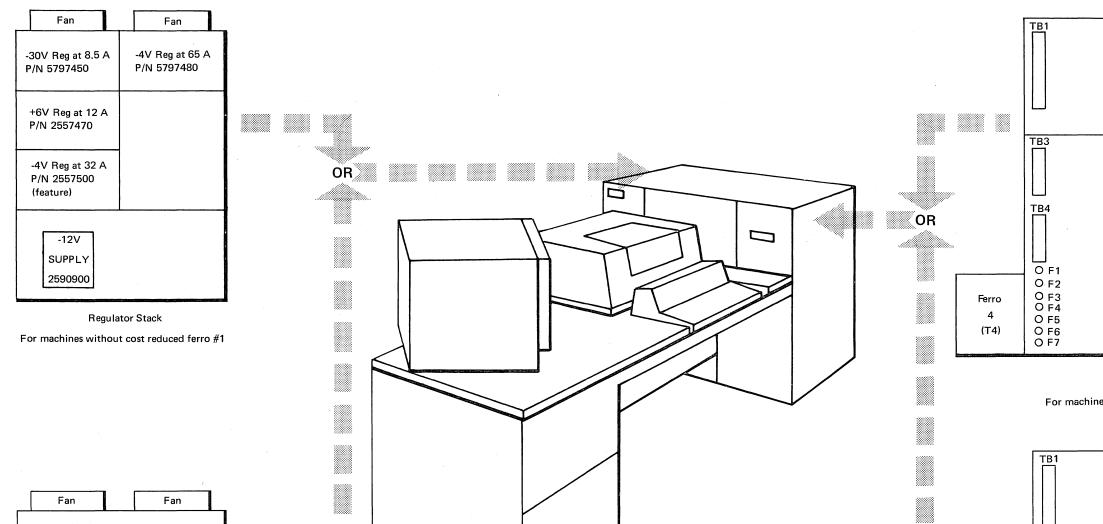

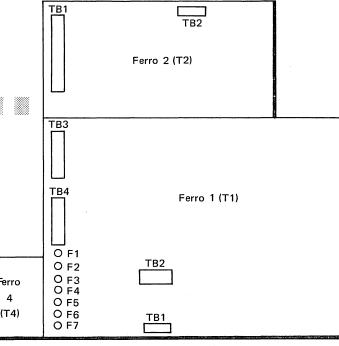

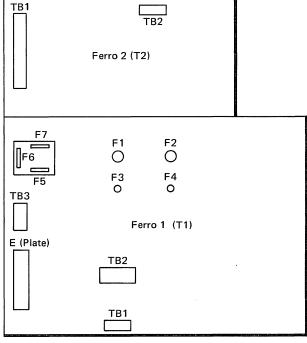

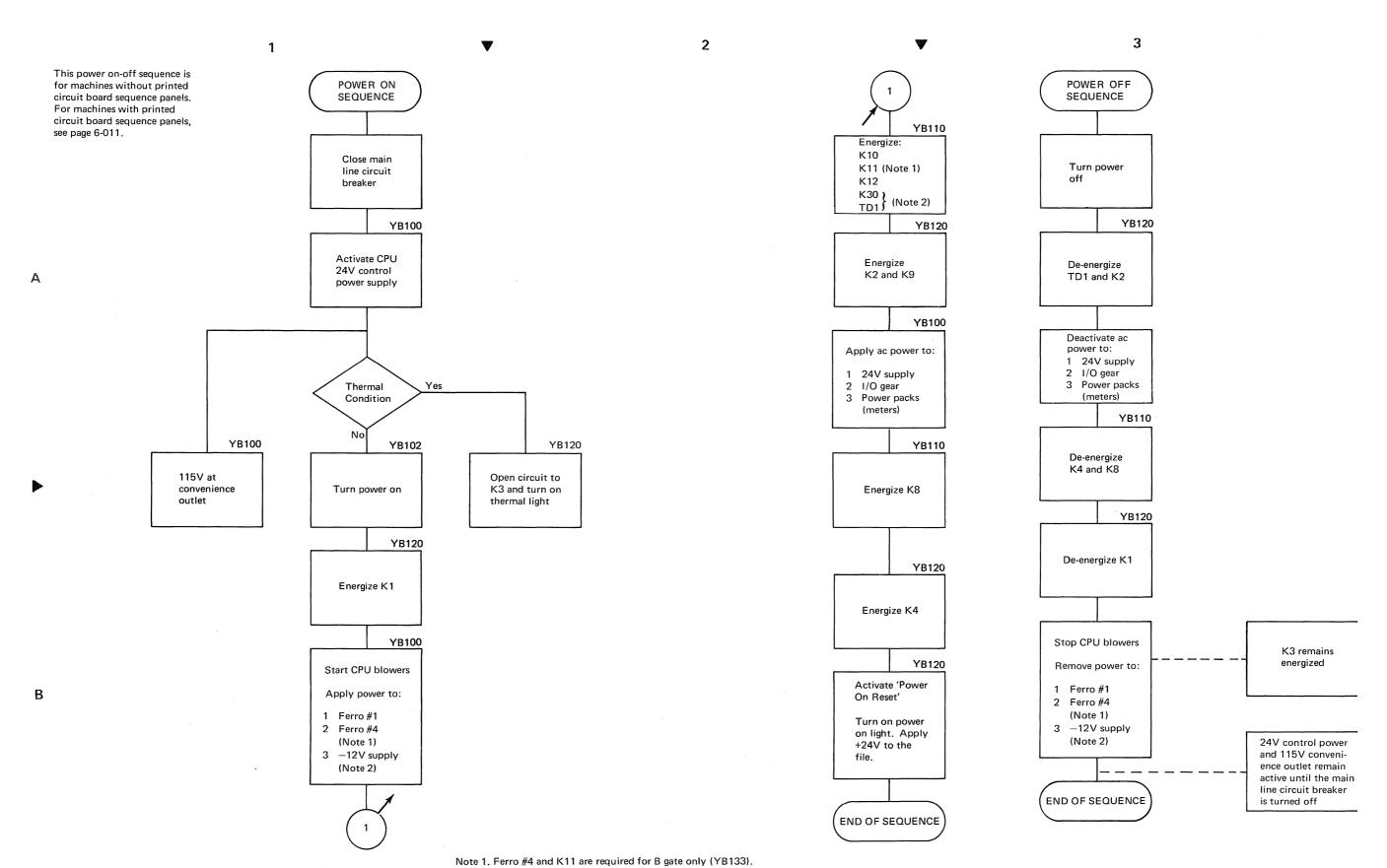

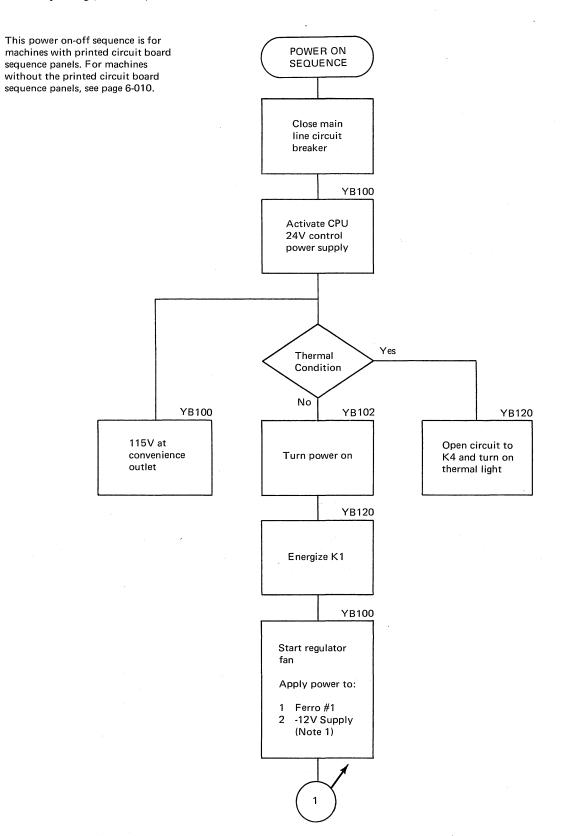

## Chapter 5. Power and Cooling 1-501

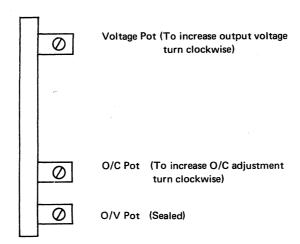

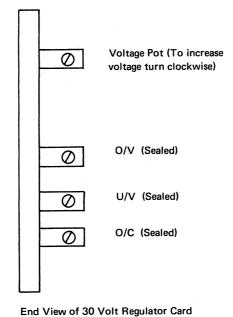

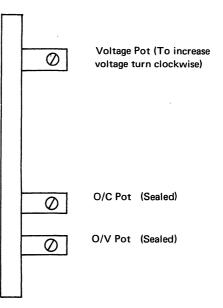

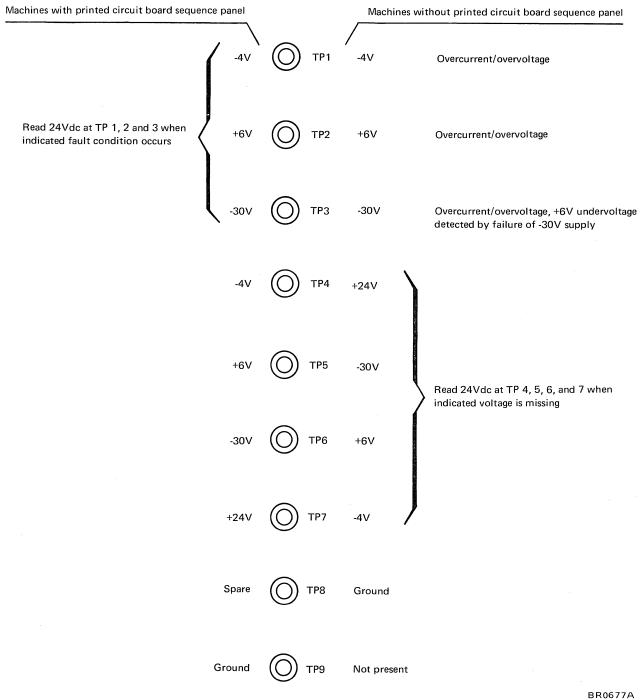

Power Input, Output, Sequencing, and MST Regulators 1-501

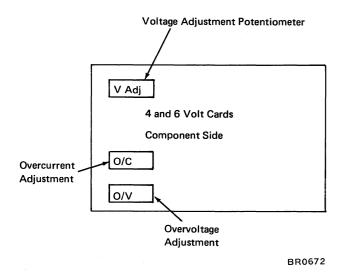

-4 Volt and +6 Volt Power Supplies 1-502

Power Supply Test Points 1-503

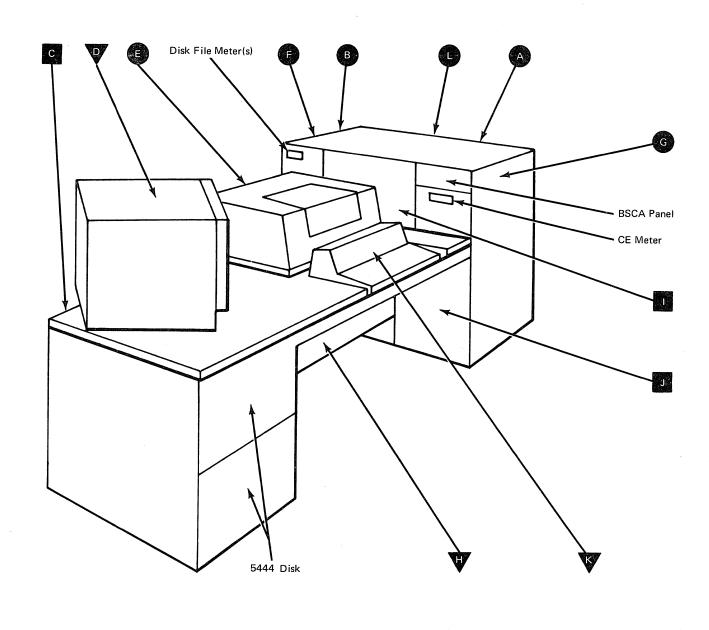

## Chapter 6. Locations 1-601

Covers and Panels 1-601

Logic Gates 1-602

Power Supplies 1-603

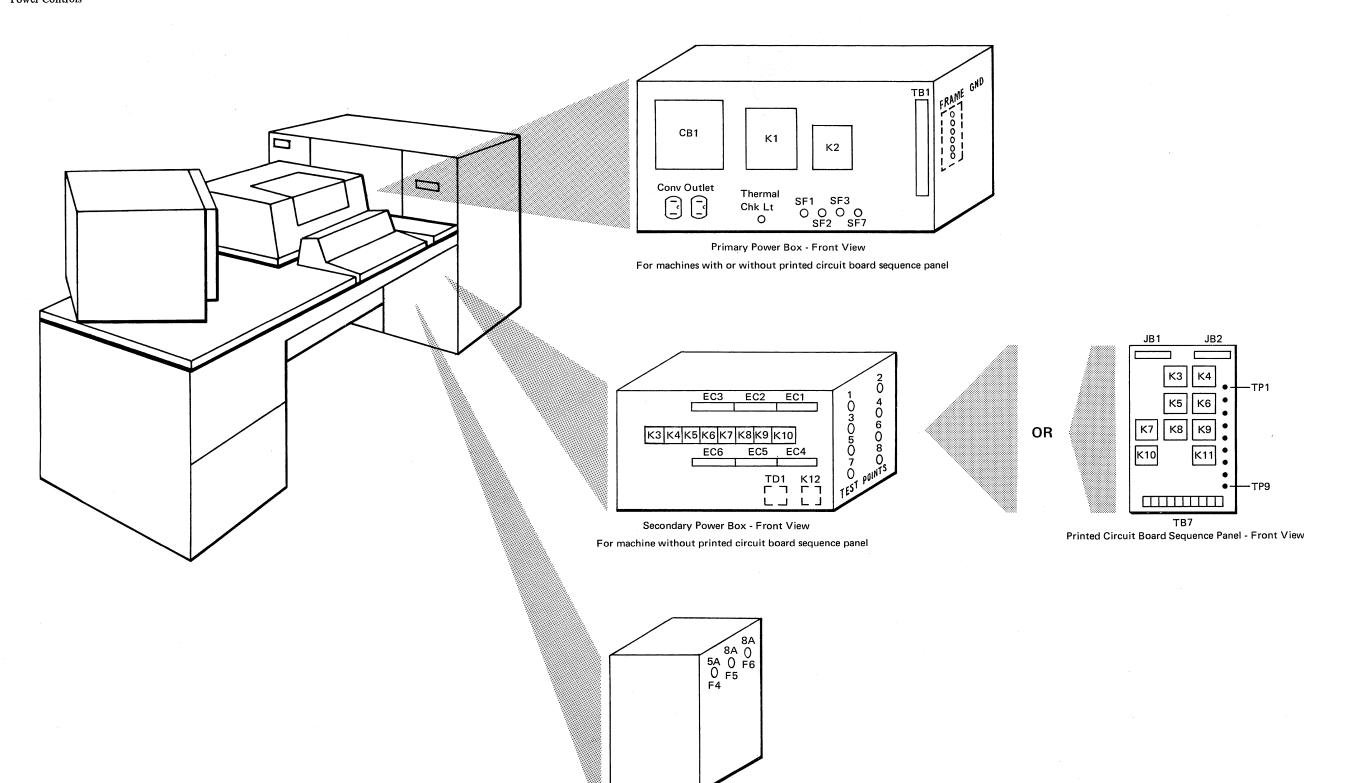

Power Controls 1-604

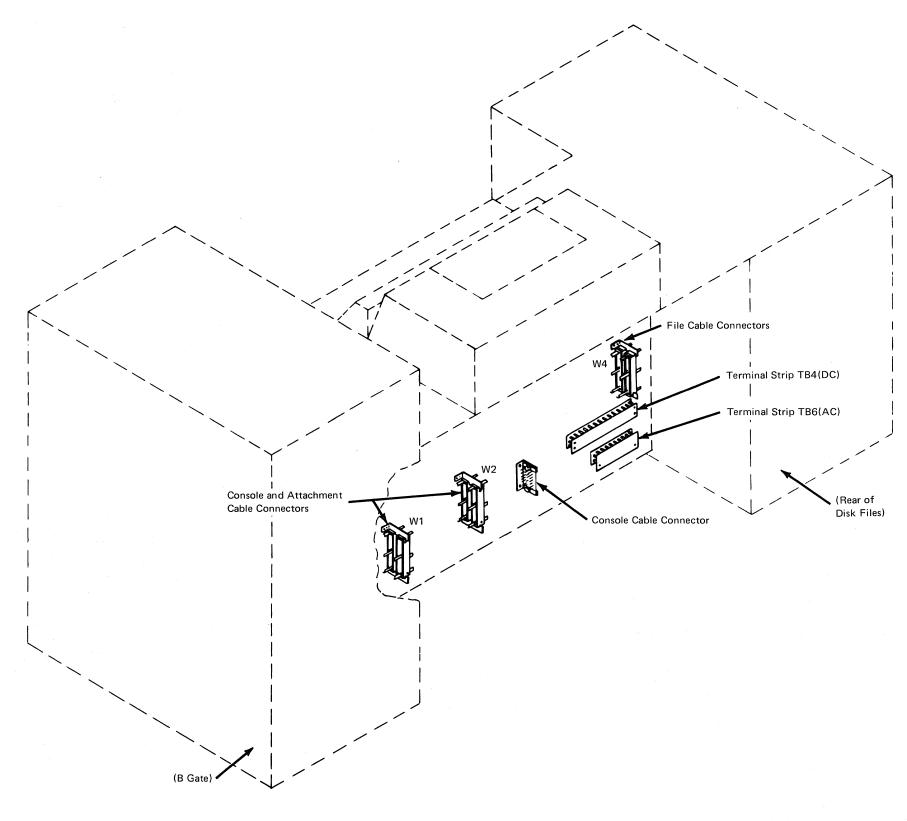

Power and Cable Channel 1-605

# Appendix A. Special Circuits 1-A1

Appendix B. World Trade 1-B1

5406 FETMM (6/70) SYSTEM MAINTENANCE-Safety

# Safety

## PERSONAL SAFETY

Ensure your own safety by making it an everyday practice to use caution at all times and by being aware of potentially dangerous areas of the machine. Be sure to read and follow the safety suggestions in Form No. 229-1264, a pocket-sized card issued to all IBM Customer Engineers.

Remember:

- Loose clothing can become entangled in moving parts of the machine.

- Drive belts, because of their internal cable construction, can cause serious injury. Do not crank a machine by pulling on the drive belts.

- Heat sinks are at an electrical potential. Do not short heat sinks to each other or to the machine side frame.

- Always unplug machine power and wait one full minute before attempting repairs or adjustments in the power supply area.

- Voltages developed in the resonant circuit of regulating power supplies are apt to be much greater than the line voltages.

- Follow the specific safety precautions that accompany many of the adjustment procedures in this manual.

# **EQUIPMENT SAFETY**

## Electrical

Always replace blown fuses with fuses of the same type and rating. Using fuses of a different type or higher rating could result in component damage. Remove power from the machine before replacing MST cards, magnets, or solenoids. Failure to do this could result in damage to a card being replaced or to other cards in the net.

## Mechanical

Do not operate the machine under power with units disassembled, removed, or maladjusted. Keep tools clear of the mechanism when the machine is operating under power.

# CAUTION

Do not use IBM cleaning fluid on plastic parts.

# Chapter 1. Reference Data

This section contains charts, listings, and diagrams giving general information for diagnosing system failures.

The following sections of this manual (sections 2 through 11) contain the flowcharts, timing charts, and diagrams for the central processing unit and attachments. The reference material found in this chapter is a collection of the most frequently used data found in these chapters. For more detailed information on any of the data found in this chapter, refer to the chapter that fully explains the area that you are working on.

For diagnostic techniques, refer to the maintenance analysis procedures (MAP) chart user's guide. The MAP charts help to isolate machine troubles without the use of an oscilloscope.

|                                            | Mnem                                                                 | Ор                                                             | Q                                                              | Opera                                     | nds                                      |                         | Comments                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------|------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Two Address<br>Instruction                 | ZAZ<br>AZ<br>SZ<br>MVX<br>ED<br>ITC<br>MVC<br>CLC<br>ALC<br>SLC      | X4<br>X6<br>X7<br>X8<br>XA<br>XB<br>XC<br>XD<br>XE<br>XF       | L1L2<br>L1L2<br>L1L2<br>L1<br>L1<br>L1<br>L<br>L               |                                           |                                          |                         | Zero and add zoned Add zoned decimal Subtract zoned decimal Move hex characters Edit Insert and test characters Move characters Compare logical characters Add logical characters Subtract logical characters                                                                                                                                         |

|                                            |                                                                      | 0<br>1<br>2<br>4<br>5<br>6<br>8<br>9                           |                                                                | 0                                         | p1 p1 p1 Op2 Op2 Op2 Op2 Op2 Op2 Op2 Op2 | Op2<br>Op2<br>Op2<br>o2 | Op1 direct, Op2 direct Op1 direct, Op2 indexed by XR1 Op1 direct, Op2 indexed by XR2 Op1 indexed by XR1, Op2 direct Op1 indexed by XR1, Op2 indexed by XR1 Op1 indexed by XR1, Op2 indexed by XR2 Op1 indexed by XR1, Op2 indexed by XR2 Op1 indexed by XR2, Op2 direct Op1 indexed by XR2, Op2 indexed by XR1 Op1 indexed by XR2, Op2 indexed by XR1 |

| One Address<br>Instruction<br>(Non-Branch) | SNS<br>LIO<br>ST<br>L<br>A<br>TBN<br>TBF<br>SBN<br>SBF<br>MVI<br>CLI | Y0<br>Y1<br>Y4<br>Y5<br>Y6<br>Y8<br>Y9<br>YA<br>YB<br>YC<br>YD | DA¦M¦N<br>DA¦M;N<br>Reg<br>Reg<br>Mask<br>Mask<br>Mask<br>Mask |                                           |                                          |                         | Sense I/O Load I/O Store register Load register Add to register Test bits on Test bits off Set bits on Set bits off Move logical immediate Compare logical immediate                                                                                                                                                                                  |

| One Address<br>Instruction<br>(Branch)     | BC<br>TIO<br>LA                                                      | 3<br>7<br>8<br>Z0<br>Z1<br>Z2                                  | Cond. DA M¦N Bit 6-XR Bit 7-XR                                 | _                                         | Addr                                     |                         | Op1 direct Op1 indexed by XR1 Op1 indexed by XR2 Branch on condition Test I/O and branch Load address                                                                                                                                                                                                                                                 |

| Command<br>Instruction                     | HPL<br>APL<br>JC                                                     | C D E F0 F1 F2 F3                                              | Tens DA MIN Cond.                                              | Op2 Op2 Op2 Unit N U Numbe bytes t Contro | o jump                                   |                         | Op2 direct Op2 indexed by XR1 Op2 indexed by XR2 Halt program level Advance program level Jump on condition Start I/O                                                                                                                                                                                                                                 |

| -             |     |      |    |     |                  |   |    | - Op C<br>(one l                       |                          |     |     |     |     |                                        | :   | · · · · · · · · · · · · · · · · · · ·  | Q<br>Code   |              | perands ———                  | Total<br>Instr<br>Length | Туре |

|---------------|-----|------|----|-----|------------------|---|----|----------------------------------------|--------------------------|-----|-----|-----|-----|----------------------------------------|-----|----------------------------------------|-------------|--------------|------------------------------|--------------------------|------|

| Bits<br>0 - 3 | -   |      |    |     |                  |   |    | - Bits 4                               | 1 - 7                    |     |     |     |     |                                        |     | -                                      | One<br>Byte | First ——     | Second——                     | Longin                   |      |

|               | 0   | 1    | 2  | 3   | 4                | 5 | 6  | 7                                      | 8                        | 9   | А   | В   | С   | D                                      | Е   | F                                      |             |              |                              |                          |      |

| 0             |     |      |    |     |                  |   |    |                                        | //////<br>MVX<br>/////// |     | ED/ | ITC | MVC | ////////////////////////////////////// | ALC | ////////////////////////////////////// |             |              | 2 Bytes Direct               | 6                        | х    |

| 1             |     |      |    |     | (//////<br>ZAZ// |   |    |                                        | ///////<br>/MVX          |     | ED  | ITC | MVC | cLc                                    | ALC | SLC                                    |             | 2 Bytes      | 1 Byte Disp.<br>Index by XR1 | 5                        | ×    |

| 2             |     |      |    | -   | ZAZÍ             |   |    |                                        | MVX                      |     | ED  | ITC | MVC | CLC                                    | ALC | SLC                                    |             | Direct       | 1 Byte Disp.<br>Index by XR2 | 5                        | х    |

| 3             | SNS | LIO  |    |     | ST               | L | A  |                                        | TBN                      |     | SBN | SBF | MVI | CLI                                    |     |                                        |             |              |                              | 4                        | Y    |

| 4             |     |      |    |     | ZAZ              | - |    | ////////////////////////////////////// | MVX                      |     | ED/ | ITC |     |                                        | ALC | SLC                                    |             | 1 Byte       | 2 Bytes Direct               | 5                        | ×    |

| 5             |     |      |    |     |                  |   |    |                                        | MVX                      |     | ED  | ITC | MVC | ////////////////////////////////////// | ALC | ////////////////////////////////////// |             | Displacement | 1 Byte Disp.<br>Index by XR1 | 4                        | ×    |

| 6             |     |      |    |     | (ZAZ)            |   | AZ |                                        | MVX                      |     | ED  | ITC | MVC | CLC                                    | ALC | SLC                                    |             | Indexed      | 1 Byte Disp.<br>Index by XR2 | 4                        | ×    |

| 7             | SNS | :LIO | .A | ,   | ST               | L | A  |                                        | TBN                      | TBF | SBN | SBF | MVI | CLI                                    |     |                                        |             | By XR1       |                              | 3                        | Y    |

| 8             |     |      |    |     | ZAZ              |   | AZ | //sz/                                  | MVX                      |     | ED  | ITC | MVC | CLC                                    | ALC | SLC                                    |             | 1 Byte       | 2 Bytes Direct               | 5                        | ×    |

| 9             |     |      |    |     | ZAZ              |   | AZ |                                        | MVX                      |     | ED  | ITC | MVC | CLC                                    | ALC | SLC                                    |             | Displacement | 1 Byte Disp.<br>Index by XR1 | 4                        | x    |

| Α             |     |      |    |     | ZAZ              |   | AZ |                                        | MVX                      |     | ED  | ITC | MVC | cLC                                    | ALC | SLC                                    |             | Indexed      | 1 Byte Disp.<br>Index by XR2 | 4                        | ×    |

| В             | SNS | LIO  |    | -   | ST               | L | Α  |                                        | TBN                      | TBF | SBN |     | MVC |                                        |     |                                        |             | By XR2       |                              | 3                        | Y    |

| С             | BC  | TIO  | LA |     |                  |   |    |                                        |                          |     |     |     |     |                                        |     |                                        |             |              | 2 Bytes Direct               | 4                        | z    |

| D             | BC  | TIO  | LA |     | -                |   |    |                                        |                          |     |     |     |     |                                        |     | ,                                      |             |              | 1 Byte Disp.<br>Index by XR1 | 3                        | z    |

| E             | ВС  | TIO  | LA |     |                  |   |    |                                        |                          |     |     |     |     |                                        |     |                                        |             |              | 1 Byte Disp.<br>Index by XR2 | 3                        | z    |

| F             | HPL | APL  | JC | SIO |                  |   |    |                                        |                          |     |     |     |     |                                        |     |                                        |             |              |                              | 3                        | F    |

Legend

OP BITS 0123

X 2 address instruction (can be indexed by bits 0-3)

Y 1 address instruction (can be indexed by bits 0 and 1)

Z 1 address instruction (can be indexed by bits 2 and 3)

F Command instruction

| OF   AZ   X                                  | Op             | Mnem              | Ор          | Q           | R | X <sub>1</sub> | Н1          | L <sub>1</sub> | X <sub>2</sub> | H <sub>2</sub> | L <sub>2</sub> | Α           | В           | Ор                   | Mnem                     | Ор          | Q           | R | X <sub>1</sub> | Н1 | L <sub>1</sub> | X <sub>2</sub> | H <sub>2</sub> | L <sub>2</sub> | Α           | В           | 1 | Ор             | Mnem              | Ор          | Q           | R      | X <sub>1</sub> | H <sub>1</sub> | L <sub>1</sub> | X <sub>2</sub> | H <sub>2</sub> | L <sub>2</sub> | А                | В                |

|----------------------------------------------|----------------|-------------------|-------------|-------------|---|----------------|-------------|----------------|----------------|----------------|----------------|-------------|-------------|----------------------|--------------------------|-------------|-------------|---|----------------|----|----------------|----------------|----------------|----------------|-------------|-------------|---|----------------|-------------------|-------------|-------------|--------|----------------|----------------|----------------|----------------|----------------|----------------|------------------|------------------|

| 08   TC                                      | 06<br>07<br>08 | AZ<br>SZ<br>MVX   | x<br>x<br>x | x<br>x<br>x |   |                | ×<br>×<br>× | ×<br>×<br>×    |                | x<br>x<br>x    | ×<br>×<br>×    | x<br>x<br>x | x<br>x<br>x | 4C<br>4D<br>4E       | MVC<br>CLC<br>ALC        | x<br>x<br>x | ×<br>×<br>× |   | x<br>x<br>x    |    |                |                | x<br>x<br>x    | x<br>x<br>x    | x<br>x<br>x | x<br>x<br>x |   | 96<br>97<br>98 | AZ<br>SZ<br>MVX   | x<br>x<br>x | x<br>x<br>x |        | x<br>x<br>x    | ٠              |                | x<br>x<br>x    |                |                | X<br>X<br>X      | x<br>x<br>x<br>x |

| 14   ZAZ                                     | 0B<br>0C<br>0E | MVC<br>CLC<br>ALC | X<br>X<br>X | x<br>x<br>x |   |                | ×<br>×<br>× | ×<br>×<br>×    |                | x<br>x<br>x    | ×<br>×<br>×    | ×           | x<br>x<br>x | 54<br>56<br>57       | ZAZ<br>AZ<br>SZ          | ×<br>×<br>× | ×××         |   | ×<br>×<br>×    |    |                | x<br>x         | X              | X              | x<br>x      | ×<br>×<br>× |   | 9B<br>9C<br>9D | ITC<br>MVC<br>CLC | ×<br>×<br>× | x<br>x<br>x |        | x<br>x<br>x    |                |                | ×<br>×<br>×    |                |                | x<br>x<br>x<br>x | ×<br>×<br>×<br>× |

| 17   SZ                                      | 14             | ZAZ               | ×           | ×           |   |                | ×           | ×              | 1              | ×              | ×              | ×           | ×           | 5A<br>5B<br>5C       | ED<br>ITC<br>MVC         | x<br>x      | ×           |   | x<br>x         |    |                | ×<br>×         |                | ·              | ×           | ×<br>×      |   | Α4             | ZAZ               | ×           | x           |        | ×              |                |                | ×              |                |                | x<br>x<br>x      | ×                |

| 1 C MVC                                      | 17<br>18<br>1A | SZ<br>MVX<br>ED   | x<br>x      | ×           |   |                | ×           | x<br>x         | ×              |                |                | ×<br>×      | ×           | 5E<br>5F             | ALC<br>SLC               | ×           | х           | - | ×              |    |                | ×              | ē.             | -              | х           | ×           |   | A7<br>A8<br>AA | SZ<br>MVX<br>ED   | ×<br>×<br>× | x<br>x<br>x |        | x<br>x<br>x    |                |                | ×<br>×         |                |                | x<br>x<br>x      | x<br>x<br>x      |

| 24                                           | 10<br>10<br>16 | MVC               | x<br>x<br>x | ×<br>×      |   |                | ×           | x<br>x<br>x    | ×<br>×<br>×    |                |                | x<br>x<br>x | X<br>X      | 66<br>67<br>68       | AZ<br>SZ<br>MVX          | ×<br>×<br>× | ×<br>×<br>× |   | x<br>x<br>x    |    |                | ×<br>×<br>×    |                |                | x<br>x<br>x | x<br>x<br>x |   | AC<br>AD<br>AE | MVC<br>CLC<br>ALC | ×           | x<br>x<br>x |        | x<br>x<br>x    |                |                | ×<br>×         |                |                | x<br>x<br>x      | x<br>x<br>x      |

| 28 MVX x x x x x x x x x x x x x x x x x x x | 26<br>27       | ZAZ<br>AZ<br>SZ   | х           | ×           |   |                | ×           | ×              | ×              |                |                | ×           | x           | 6B<br>6C             | ITC<br>MVC               | ×           | x<br>×      |   | x<br>x         |    |                | ×              |                |                | x<br>x      | ×           |   | В1             | LIO               | ×           | ×           |        | ×              |                |                |                |                |                |                  | x<br>x<br>x      |

| 2D   CLC   x   x   x   x   x   x   x   x   x | 28<br>2A<br>2B | MVX<br>ED<br>ITC  | X<br>X      | ×<br>×      |   | -              | ×           | x<br>x         | ×              |                |                | ×           | x<br>x      | 6F                   | SLC                      | x           | ×           |   | ×              |    |                |                |                |                | 1           | x           |   | В6<br>В8       | A<br>TBM          | x<br>x      | x<br>x      |        | x<br>x         |                |                |                |                |                |                  | x<br>x<br>x<br>x |

| 30 SNS                                       | 2E             | CLC               | x<br>x      | ×           |   |                | ×           | x<br>x         | x              |                |                | ×           | x<br>x      | 71<br>74<br>75       | LIO<br>ST<br>L           | x<br>x<br>x | ×<br>×<br>× |   | x<br>x<br>x    |    |                |                | -              |                |             | x<br>x<br>x |   | BA<br>BB<br>BC | SBN<br>SBF<br>MVI | ×<br>×<br>× | x<br>x<br>x |        | ×              |                |                |                |                |                |                  | x<br>x<br>x      |

| 36   A                                       | 31<br>34       | LIO<br>ST         | ×           | ×           |   |                | ×           | ×              |                |                |                |             | x<br>x      | 78<br>79<br>7A       | TBN<br>TBF<br>SBN        | x<br>x<br>x | ×<br>×<br>× |   | X<br>X<br>X    |    |                |                |                |                |             | x<br>x<br>x |   | C0<br>C1       | BC<br>TIO         | ×           | x<br>x      |        |                | ×              | х              |                |                |                |                  | -                |

| 3B   SBF   x   x   x   x   x   x   x   x   x | 36<br>38<br>39 | A<br>TBN<br>TBF   | x<br>x<br>x | ×<br>×      |   |                | ×           | ×              |                |                |                |             | x<br>x      | 7C<br>7D             | MVI<br>CLI               | ×           | ×           |   | X<br>X         |    |                |                | ×              | ×              | ×           | ×           |   | D0<br>D1       | BC<br>TIO         | ×           | x<br>x      |        | ×              |                |                |                |                |                |                  |                  |

| 44   ZAZ   x   x                             | 3B             | SBF               | x<br>x      | ×           |   |                | ×           | x<br>x         |                |                |                |             | x<br>x      | 86<br>87<br>88       | AZ<br>SZ<br>MVX          | x<br>x<br>x | ×<br>×<br>× | · | x<br>x<br>x    |    |                |                | x<br>x         | ×<br>×<br>×    | ×<br>×<br>× | ×<br>×      |   | E0<br>E1       | BC<br>TIO         | ×           | x<br>x      |        | x<br>x         |                |                |                |                |                |                  |                  |

| 48 MVX   x   x                               | 46<br>47<br>48 | AZ<br>SZ<br>MVX   | x<br>x<br>x | ×<br>×<br>× |   | ×              |             |                |                | x<br>x<br>x    | x<br>x<br>x    | x<br>x<br>x | x<br>x<br>x | 8B<br>8C<br>8D<br>8E | ITC<br>MVC<br>CLC<br>ALC | ×<br>×<br>× | ×<br>×<br>× |   | x<br>x<br>x    |    |                |                | x<br>x<br>x    | ×<br>×<br>×    | ×<br>×<br>× | ×<br>×<br>× |   | F0<br>F1<br>F2 | HPL<br>APL<br>JC  | x<br>x<br>x | ×<br>×<br>× | x<br>x |                |                |                |                |                |                |                  |                  |

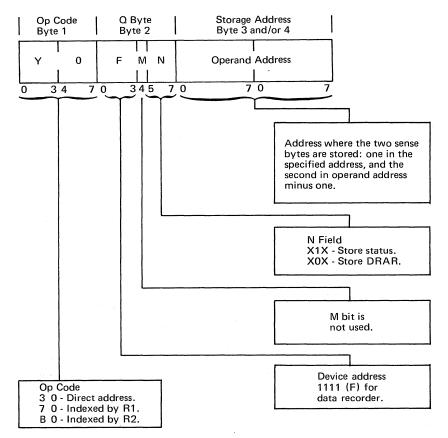

| Op Code                  | Q    | Code |                                               | Add                  | lress | Op Code Q Code D1 Indexed                                                                                                                                                                                   |

|--------------------------|------|------|-----------------------------------------------|----------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Z1                       | DA   | М    | N                                             | Opera                |       | Z1 DA M N Displacement                                                                                                                                                                                      |

| 0 7                      | 8 11 | 12   | 13 15                                         | 16                   | XX    |                                                                                                                                                                                                             |

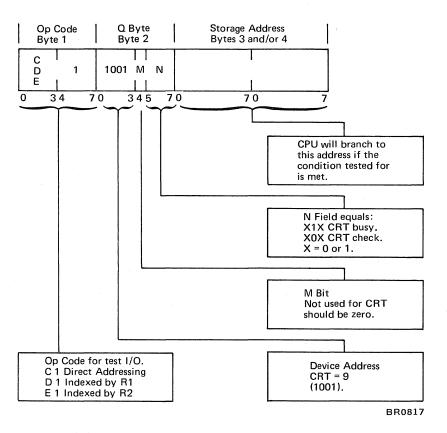

| C1<br>D1<br>E1           |      |      |                                               | 2 By<br>1 By<br>1 By | /te   | Direct Addressing (H1L1) Indexed by XR1 Indexed by XR2                                                                                                                                                      |

|                          | E    |      |                                               |                      |       | Device Address Serial Printer                                                                                                                                                                               |

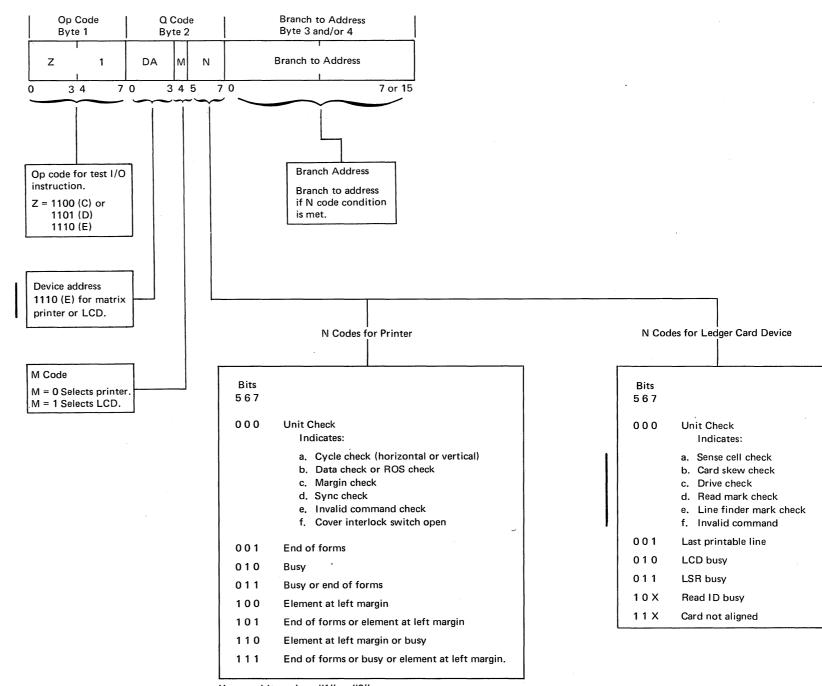

| 5213/<br>2222<br>Printer |      | 0    | 000<br>001<br>010<br>011<br>100<br>101<br>110 |                      |       | Selects Printer Unit Check End of Forms Busy Busy or End of Forms Element at Left Margin End of Forms or Element at Left Margin Element at Left Margin or Busy End of Forms, Element at Left Margin or Busy |

|                          |      | 1    | 000<br>001<br>010<br>011<br>10X<br>11X        | xxxx                 | xxxx  | Selects LCD Unit Check Last Printable Line LCD Busy LSR Busy Read ID Busy Card Not Aligned Branch to address if condition met                                                                               |

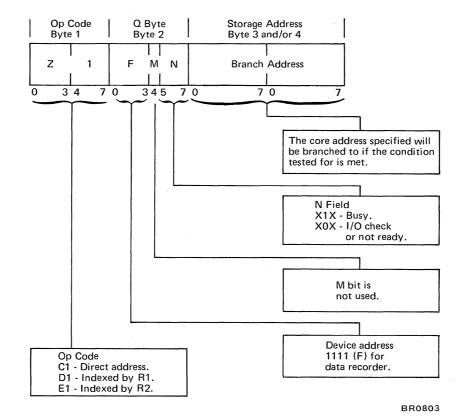

|                          | F    |      |                                               |                      |       | Device Address Data Recorder                                                                                                                                                                                |

| 5496<br>Data<br>Recorder |      | 0    | X1X<br>X0X                                    | xxxx                 | xxxx  | M bit is not used, it should be zero.<br>Busy<br>I/O Check or Not Ready<br>Branch to address if condition met                                                                                               |

|                          | 9    |      |                                               |                      |       | Device Address CRT                                                                                                                                                                                          |

| 2265<br>CRT              | -    | 0    | X1X<br>X0X                                    | xxxx                 | xxxx  | M Bit is not used, it should be zero.<br>CRT Busy<br>CRT Check (D Reg Parity Error or CRT Not Ready)<br>Branch to address if condition met                                                                  |

| 5406                     | 1    |      |                                               |                      |       | Device Address Keyboard                                                                                                                                                                                     |

| Keyboard                 |      |      |                                               | nvalid ar            |       |                                                                                                                                                                                                             |

|                          | Α    |      |                                               |                      |       | Device Address Drive 1 (Spindle 0)                                                                                                                                                                          |

| 5444                     | В    |      |                                               |                      |       | Device Address Drive 2 (Spindle 1)                                                                                                                                                                          |

| File                     |      | 0    | 000<br>010<br>100                             |                      |       | M bit is not used.<br>Not Ready or Error<br>Busy-Data Transfer in Process<br>Scan Found                                                                                                                     |

|                          | 8    |      |                                               |                      |       | Device Address BSCA                                                                                                                                                                                         |

| BSCA                     |      | 0    | 000<br>001<br>010<br>011<br>100<br>110        |                      |       | M bit is not used.<br>Not Ready/Unit Check<br>Op End Interrupt<br>Busy<br>ITB Interrupt<br>Interrupt Pending<br>New Data                                                                                    |

|                          | 3    |      |                                               |                      |       | Device Address SIOC                                                                                                                                                                                         |

| SIOC                     |      | 0    | 000<br>010                                    |                      |       | M bit is not used.<br>SIOC Not Ready<br>SIOC Busy                                                                                                                                                           |

|                          |      |      |                                               | xxxx                 | VVVV  | Branch to address if condition met                                                                                                                                                                          |

Note: An X means bit can be a "1" or "0".

BR0614A

| Op Code                  |      | Q Cod | e                                             | Add                  | ress  | Op Code Q Code D1                                                                                                                  |

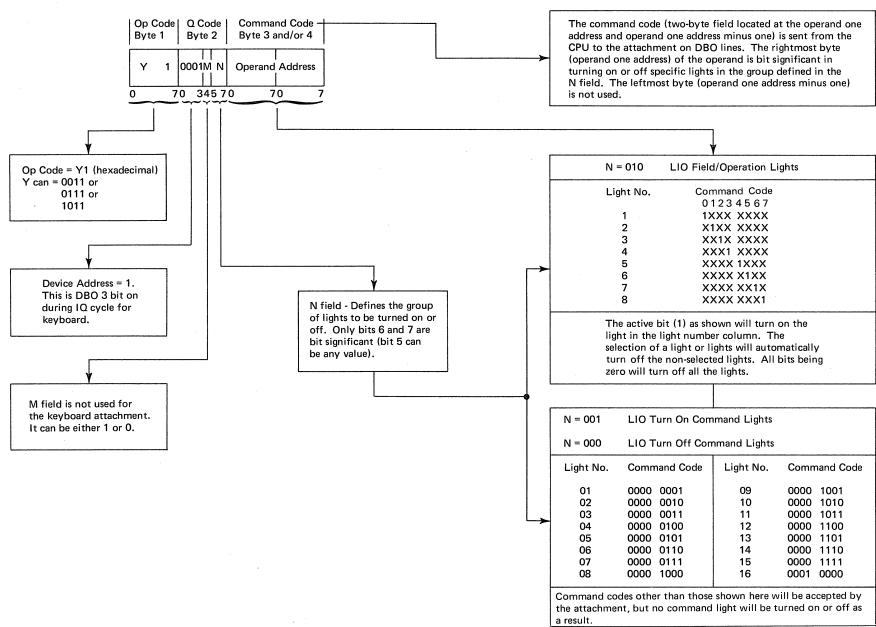

|--------------------------|------|-------|-----------------------------------------------|----------------------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| Y1                       | DA   | М     | N                                             | Opera                | and 1 | Y1 DA M N Displacement                                                                                                             |

| 0 7                      | 8 11 | 12    | 13 15                                         | 16                   | 23    |                                                                                                                                    |

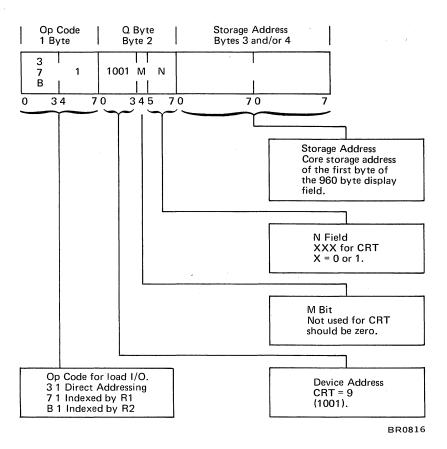

| 31<br>71<br>B1           |      |       |                                               | 2 By<br>1 By<br>1 By | 'te   | Direct Addressing (H1L1) Indexed by XR1 Indexed by XR2                                                                             |

|                          | . Е  |       |                                               |                      |       | Device Address Serial Printer                                                                                                      |

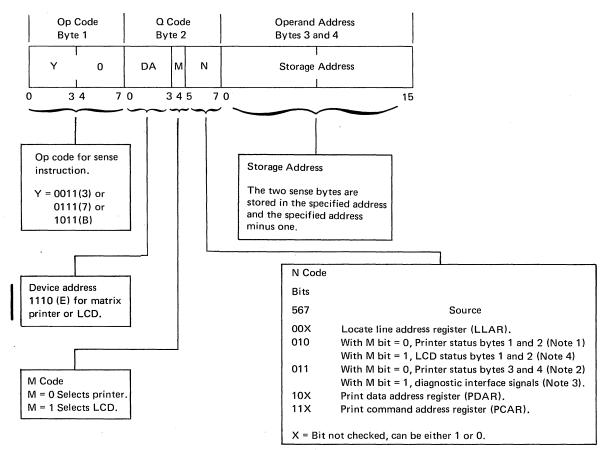

| 5213/<br>2222<br>Printer |      | 0     | 00X<br>01X<br>10X<br>11X                      |                      |       | Selects Printer Selects LCD LLAR Control LIO PDAR PCAR                                                                             |

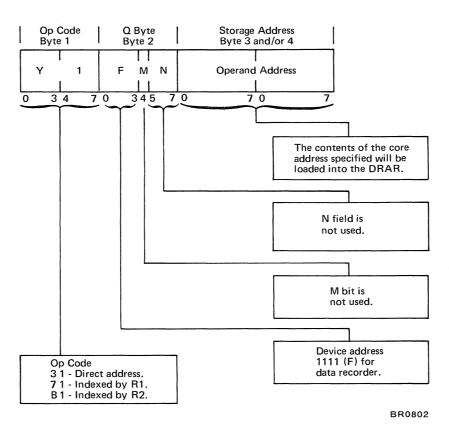

| 5496                     | F    |       |                                               |                      |       | Device Address Data Recorder                                                                                                       |

| Data<br>Recorder         |      | 0     | 000                                           |                      |       | M bit is not used, it should be zero.<br>DRAR                                                                                      |

| 2265                     | 9    |       |                                               |                      |       | Device Address CRT                                                                                                                 |

| CRT                      |      | 0     | xxx                                           |                      |       | M bit is not used, it should be zero.<br>CRTAR                                                                                     |

|                          | 1    |       |                                               |                      |       | Device Address Keyboard                                                                                                            |

| 5406<br>Keyboard         |      | X     | X00<br>X01<br>X1X                             |                      |       | M bit is not used, a zero is preferred.<br>Turn Off Command Lights<br>Turn On Command Lights<br>Turn On/Off Field/Operation Lights |

|                          | Α    |       |                                               |                      |       | Device Address Drive 1 (Spindle 0)                                                                                                 |

|                          | В    |       |                                               |                      |       | Device Address Drive 2 (Spindle 1)                                                                                                 |

| 5444<br>Disk             |      | 0     | 000<br>001<br>010<br>011<br>100<br>101<br>110 |                      |       | M bit is not used.<br>Invalid<br>Invalid<br>Invalid<br>Diagnostic CE<br>DFDR<br>Invalid<br>DFCR<br>Invalid                         |

|                          | 3    |       |                                               |                      |       | Device Address SIOC                                                                                                                |

| SIOC                     | :    | 0     | 001<br>010<br>100<br>101                      |                      |       | M bit is not used.<br>I/O Function Register<br>SIOC Length Count Register<br>SIAR<br>Data Transfer Register                        |

|                          | 8    |       |                                               |                      |       | Device Address BSCA                                                                                                                |

| BSCA                     |      | 0     | 001<br>010<br>100<br>110                      |                      |       | M bit is not used.<br>Stop Address Register<br>Transition Address Register<br>BSCAR<br>BSCAR (Diagnostic)                          |

Note: An X means bit can be a "1" or "0".

BR0615A

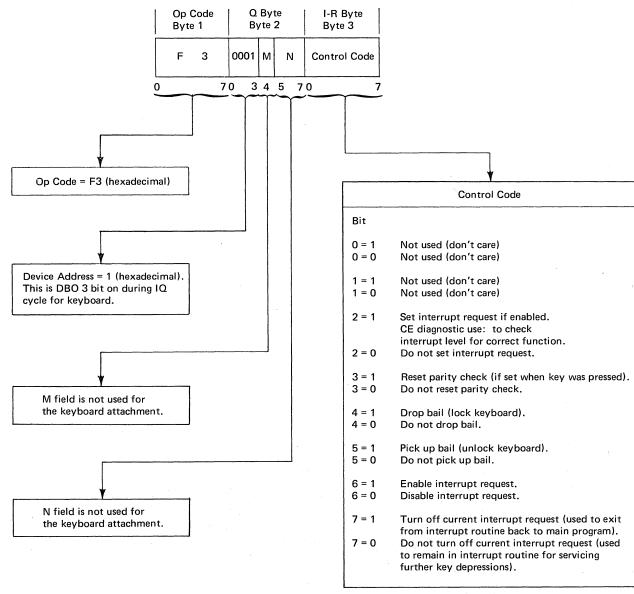

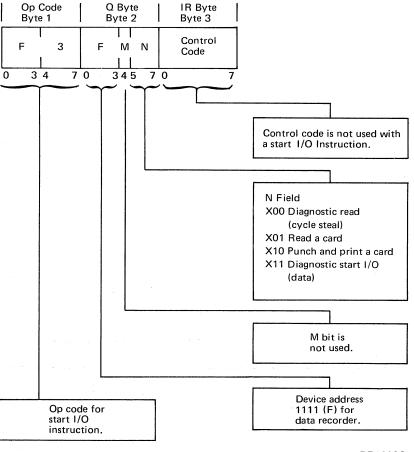

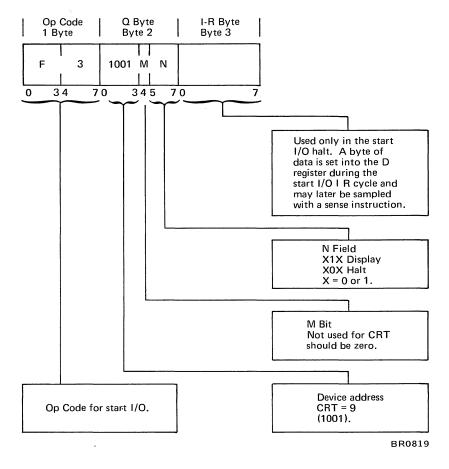

| Op Code          | Q        | Code |            | Com          | mand         |                                                                                |

|------------------|----------|------|------------|--------------|--------------|--------------------------------------------------------------------------------|

| F3               | DA       | М    | N          | Con<br>Co    |              |                                                                                |

| 0 7              | 8 11     | 12   | 13 15      | 16           | 23           |                                                                                |

|                  |          |      |            | 8421         | 8421         |                                                                                |

|                  |          |      |            |              |              |                                                                                |

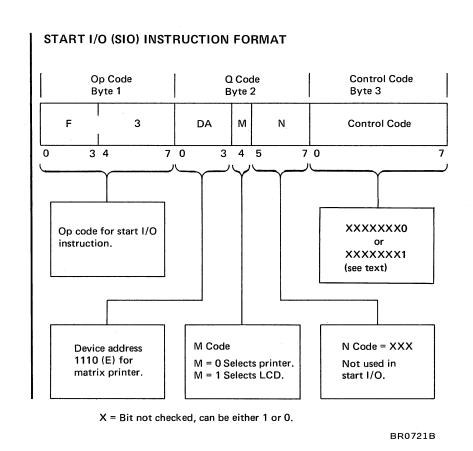

|                  | E        |      |            |              |              | Device Address Serial Printer                                                  |

|                  |          |      |            |              |              | 2 street read see serial rifficer                                              |

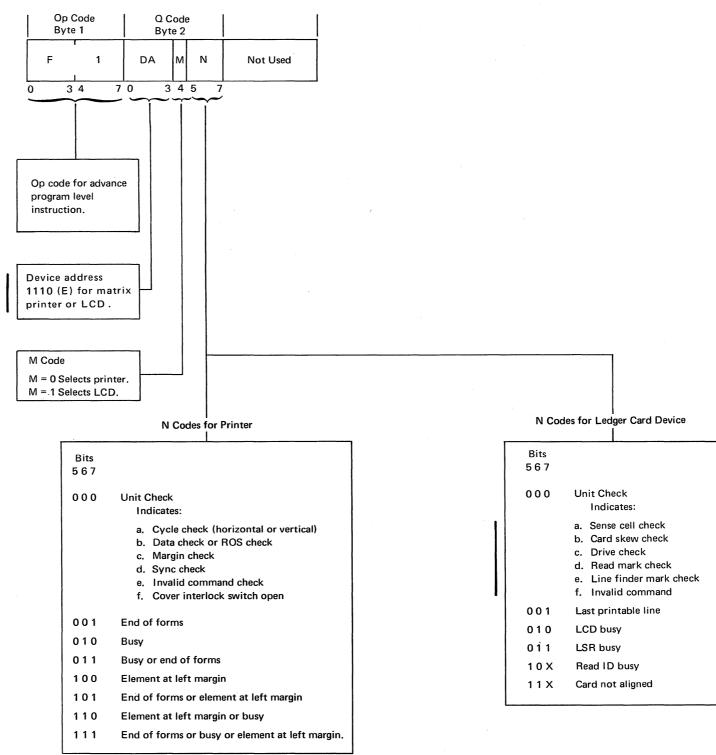

| 5213/            |          | 0    | xxx        | :            |              | Selects Printer  N field is not used, zeros are preferred.                     |

| 2222<br>Printer  |          |      |            |              | 0            | Serial Print Operation Bi-directional Print Operation                          |

|                  |          | 1    | xxx        |              | 0            | Selects LCD Start I/O (reads first command byte)                               |

|                  |          |      |            |              | 1            | Read all line finder marks (Diagnostic)                                        |

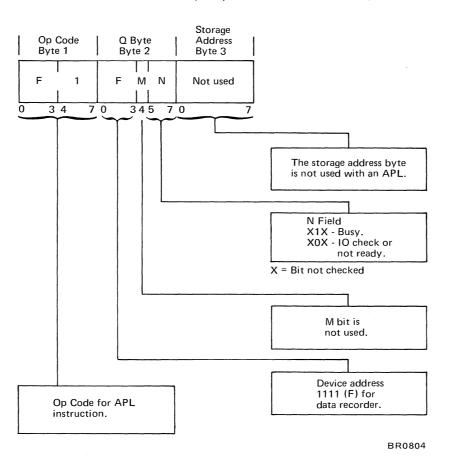

|                  | F        |      |            |              |              | Device Address Data Recorder                                                   |

| 5496             |          | 0    | X01        |              |              | M bit is not used, it should be zero.<br>Read a Card                           |

| Data<br>Recorder |          |      | X10<br>X11 |              |              | Punch a Card<br>Diagnostic Data                                                |

|                  |          |      | X00        | xxxx         | xxxx         | Diagnostic Cycle Steal                                                         |

|                  | 9        |      |            | ^^^^         | ^^^          | Device Address CRT                                                             |

| 2265             |          | 0    |            |              |              | M bit is not used, it should be zero.                                          |

| CRT              |          |      | X1X<br>X0X |              |              | Display<br>Halt                                                                |

| <u> </u>         |          |      |            | XXXX         | XXXX         | Data used in halt                                                              |

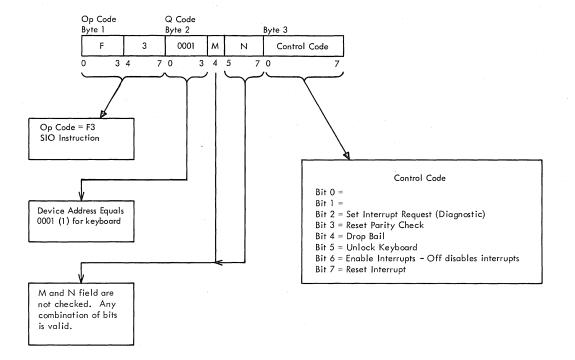

|                  | 1        |      |            |              |              | Device Address Keyboard                                                        |

|                  |          | ×    | xxx        | VV40         |              | M bit is not used, it should be zero.  N field is not used, it should be zero. |

| 5406<br>Keyboard |          | 1.   |            | XX10<br>XX01 | 0000         | CE Diagnostic (Set Interrupt Request) Reset Parity Check                       |

|                  |          |      |            | XX00         | 1000<br>0100 | Drop Bail (Lock Keyboard)<br>Pick Up Bail (Unlock Keyboard)                    |

|                  |          |      |            | XX00<br>XX00 | 0010<br>0000 | Enable Interrupt Disable Interrupt                                             |

|                  |          |      |            | XX00         | 0001         | Turn Off Current Interrupt Request                                             |

|                  | Α        |      |            |              |              | Device Address Drive 1 (Spindle 0)                                             |

|                  | В        |      |            |              |              | Device Address Drive 2 (Spindle 1)                                             |

|                  |          | 0    |            |              |              | Removable Disk<br>Fixed Disk                                                   |

| 5444             |          |      | 000        |              |              | Control Seek<br>Read                                                           |

| File             |          |      |            | XXX0         | XX00<br>XX01 | Read Data<br>Read Identifier                                                   |

|                  |          |      |            | XXX0<br>XXX0 | XX10         | Read Diagnostic                                                                |

|                  | ·        |      | 010        |              |              | Read Verify<br>Write                                                           |

|                  |          |      | 011        | XXX0         |              | Write Data<br>Write Identifier                                                 |

|                  |          |      | 011        | xxx0         | XX00         | Scan<br>Scan Equal                                                             |

|                  |          |      |            | XXX0<br>XXX0 |              | Scan Low or Equal<br>Scan High or Equal                                        |

| L                | <u> </u> | L    | L          |              | L            |                                                                                |

| Op Code | Q    | Code | 1                                      | Comn                                                                                 |                                                                                                                                      | ·<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|------|------|----------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F3      | DA   | M    | N                                      | Con<br>Co                                                                            |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0 7     | 8 11 | 12   | 13 15                                  | 16<br>8421                                                                           | 23<br>8421                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | 8    |      |                                        |                                                                                      |                                                                                                                                      | Device Address BSCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BSCA    |      | 0    | 000<br>001<br>010<br>011<br>100<br>110 | X000<br>X000<br>X000<br>X000<br>1000<br>1000<br>1010<br>1000<br>1100<br>1100<br>1000 | 0100<br>0001<br>0010<br>0000<br>0000<br>1000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000                                         | M bit must be zero. Control Start 2 Second Timeout Receive Transmit and Receive Receive Initial Auto Call Loop Test Reset Interrupt Request Enable Interrupt Disable Interrupt Cancel 2 Second Timeout Enable Reserved Mode Disable Reserved Mode Enable Step Mode Enable Test Mode Disable Test Mode Disable BSCA Disable BSCA                                                                                                                                                                                                                                                                                                           |

|         | 3    |      |                                        |                                                                                      |                                                                                                                                      | Device Address SIOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SIOC    |      | 0    | 000<br>001<br>010                      | 0000<br>0000<br>0000<br>0000<br>0001<br>0000<br>0000<br>000                          | 0001<br>0010<br>0100<br>1000<br>0000<br>0001<br>0100<br>1000<br>0000<br>0000<br>0000<br>0100<br>1000<br>1000<br>0000<br>0000<br>0000 | M bit is not used. Always Accepted Read I/O Device Write I/O Device Write I/O Device Reset Interrupt Request Enable Interrupt Disable Interrupt Reset SIOC Adapter Busy Set Interrupt Request I/O Control Byte 1 I/O 1 Select I/O 2 Select I/O 3 Select I/O 4 Select I/O 5 Select I/O 7 Select I/O 7 Select I/O 7 Select I/O 8 Select I/O 7 Select I/O 9 Select I/O 10 Select I/O 11 Select I/O 11 Select I/O 11 Select I/O 12 Select I/O 13 Select I/O 13 Select I/O 14 Select I/O 14 Select I/O 15 Select I/O 17 Select I/O 18 Select I/O 19 Select I/O 19 Select I/O 10 Select I/O 11 Select I/O 11 Select I/O 12 Select I/O 13 Select |

Note. An X means bit can be a "1" or "0".

Note. An X means bit can be a "1" or "0".

BR0616A

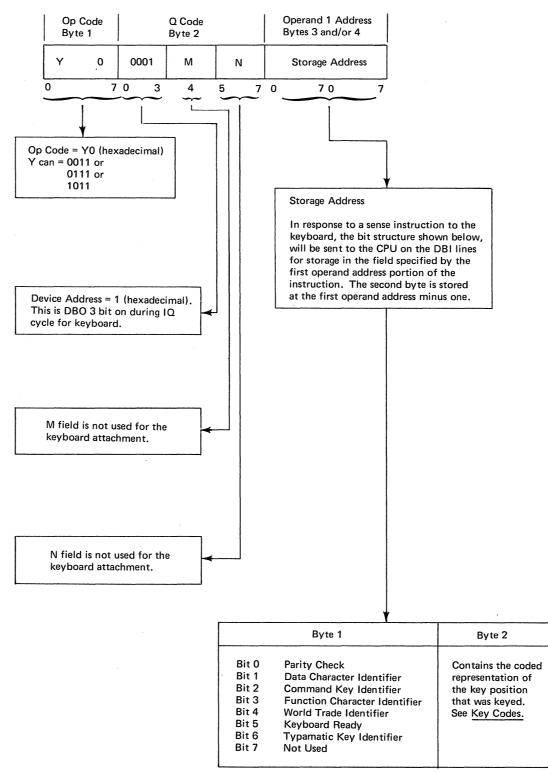

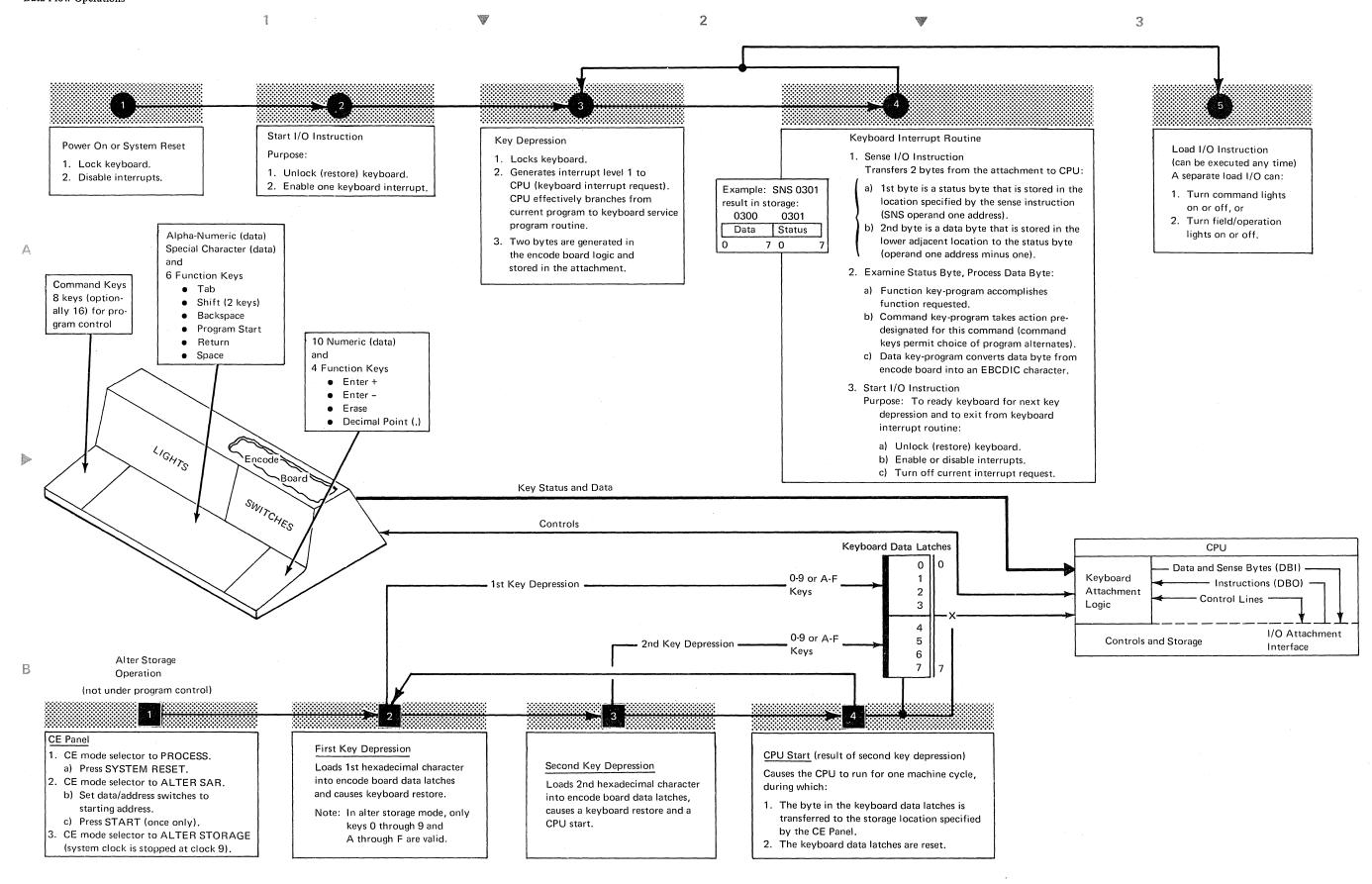

# **Keyboard Sense Instruction**

| Op Code               | (    | 2 Cod | de    | Ado                        | Iress |                                                          | Op Code                                                                                                            | Byte 1 = Opera<br>Byte 2 = Opera                                             |                              |     |             |                                                       |                     |

|-----------------------|------|-------|-------|----------------------------|-------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------|-----|-------------|-------------------------------------------------------|---------------------|

| Y0                    | DA   | М     | N     | Oper                       | and 1 |                                                          | Y0                                                                                                                 | DA                                                                           | М                            | N   | Displaceme  | nt                                                    |                     |

| 0 7<br>30<br>70<br>80 | 8 11 | 12    | 13 15 | 16<br>2 By<br>1 By<br>1 By | /te   | Index                                                    | Addressined by XR1                                                                                                 | _                                                                            |                              |     |             | <b></b>                                               |                     |

|                       | 1    |       |       |                            |       |                                                          | ice Addres                                                                                                         |                                                                              | d                            |     |             |                                                       |                     |

| 5406<br>Keyboard      |      | х     | xxx   |                            |       | N fi<br>Byt<br>0 Pa<br>1 D<br>2 Co<br>3 Fo<br>4 W<br>5 K | it is not us eld is not us e 1 arity Check ata Charac command K unction Ch orld Trade eyboard R ypamatic k ot Used | used, zero'<br>ter Identif<br>ey Identif<br>aracter Id<br>Identifier<br>eady | s are<br>ier<br>ier<br>entif | pr  | eferred.    | Byte 2 0 1 2 Contains represente the key p that was k | ation of<br>osition |

|                       |      |       |       | xxx                        | xxx   | Оре                                                      | rand Addr                                                                                                          | ess (Sense                                                                   | Byte                         | e D | estination) |                                                       |                     |

Note. An X means bit can be a "1" or "0".

BR0617A

# Printer Sense Instruction

| Op Code                  | Ċ    | Cod | е     | Add                        | iress | Op Code                                                                                                                        | 0.0                                                                  | Code                            |     | D1                                                                                                                                     |                                                                        |                                                                |                                       | d Address<br>d Address |

|--------------------------|------|-----|-------|----------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------|------------------------|

| Y0                       | DA   | М   | · N   | Oper                       | and 1 | Y0                                                                                                                             | DA                                                                   | Μľ                              | V   | Displacement                                                                                                                           | Dytt 2                                                                 | 0, ,                                                           | Ороган                                | a , (da) 555           |

| 0 7<br>30<br>70<br>80    | 8 11 | 12  | 13 15 | 16<br>2 By<br>1 By<br>1 By | /te   | Direct Addressing<br>Indexed by XR1<br>Indexed by XR2                                                                          | g (H1L1)                                                             |                                 |     |                                                                                                                                        |                                                                        |                                                                |                                       |                        |

| -                        | Е    |     |       |                            |       | Device Address                                                                                                                 | Serial Prin                                                          | ter                             |     |                                                                                                                                        |                                                                        |                                                                |                                       |                        |

|                          |      | 0   | 010   |                            |       | Select Printer Byte 1 0 Horizontal Cy 1 Data Check 2 Margin Check 3 Sync Check 4 Ros Check 5 Vertical Cycle 6 Primary Carria   | : Check<br>age EOF                                                   |                                 |     | Byte 2<br>0 Count Enc<br>1 Print Left<br>2 Matrix Cou<br>3 Matrix Cou<br>4 Matrix Cou<br>5 Printer Re<br>6 SS 2<br>7 SS 1 or SS        | Commai<br>unter Tr<br>unter Tr<br>unter Tr<br>ady                      | igger 1<br>igger 2<br>igger 4                                  | 2                                     |                        |

| 5213/<br>2222<br>Printer |      |     | 011   |                            |       | Byte 3 0 High Speed L 1 Matrix Outpu 2 Matrix Outpu 3 Matrix Outpu 4 Matrix Outpu 5 Matrix Outpu 6 Matrix Outpu 7 Matrix Outpu | t Hammer<br>t Hammer<br>t Hammer<br>t Hammer<br>t Hammer<br>t Hammer | Dr2<br>Dr3<br>Dr4<br>Dr5<br>Dr6 |     | Byte 4<br>0 SS A<br>1 SS 3<br>2 Stepper Trig<br>3 Stepper Trig<br>4 SS Z<br>5 SS Y<br>6 SS X<br>7 SS W                                 | gger A<br>gger B                                                       |                                                                |                                       |                        |

| Frinter                  |      |     | 00X   |                            |       | LLAR-Hi                                                                                                                        |                                                                      |                                 | T   | LLAR-Lo                                                                                                                                |                                                                        |                                                                |                                       |                        |

|                          |      |     | 10X   |                            |       | PDAR-Hi                                                                                                                        |                                                                      |                                 | T   | PDAR-Lo                                                                                                                                |                                                                        |                                                                |                                       |                        |

|                          |      |     | 11X   |                            |       | PCAR-Hi                                                                                                                        |                                                                      |                                 |     | PCAR-Lo                                                                                                                                |                                                                        |                                                                |                                       |                        |

|                          |      | 1   | 010   |                            |       | Select LCD Byte 1 0 Sense Amp C 1 Card Skew Ch 2 Drive Check 3 Read Mark Cl 4 5 Line Finder N 6 Card In Switc 7 Card Out Swi   | neck<br>neck<br>Mark Check<br>th On                                  | <b>(</b>                        |     | Byte 2<br>0 Sense Amp<br>1 Sense Amp<br>2 Sense Amp<br>3 Sense Amp<br>4 Timing Puls<br>5 Drive Check<br>6 Activate LO<br>7 Hold Busy S | 2<br>3<br>4<br>se<br>SS<br>D Feed                                      | Clutc                                                          | 'n                                    |                        |

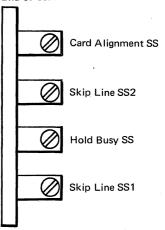

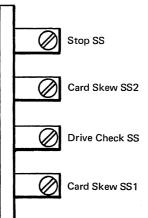

|                          |      |     | 011   |                            |       | Byte 3* 0 SS 1—Skip Li 1 SS 2—Skip Li 2 Late Mark 3 Special Tie Up 4 Card Alignme 5 Spare 6 Spare 7 Stop SS                    | ne<br>o (always d                                                    | off)                            |     | Byte 4 0 5213 Printe 1 Not Vertica 2 Not Bi-direc 3 Secondary C 4 Not Rm sw 5 Rm sw 2 Stc 6 Primary or S 7 Primary For                 | I Forms<br>ctional P<br>Carriage I<br>1 Slow a<br>op or LN<br>Secondai | Contrint For EOF and No 1 sw 1 s | eature<br>ot LM sw<br>Slow<br>ms Moti |                        |

|                          |      |     |       | xxx                        | xxx   | Operand Addres                                                                                                                 | ss (Sense E                                                          | ytes I                          | Des | tination)                                                                                                                              |                                                                        |                                                                |                                       |                        |

<sup>\*</sup> If LCD feature is not installed, then this byte will be hex 00.

Note. An X means bit can be a "1" or "0".

BR0618A

SYSTEM MAINTENANCE—Reference Data Sense Instruction (Part 1 of 3)

BR0620A

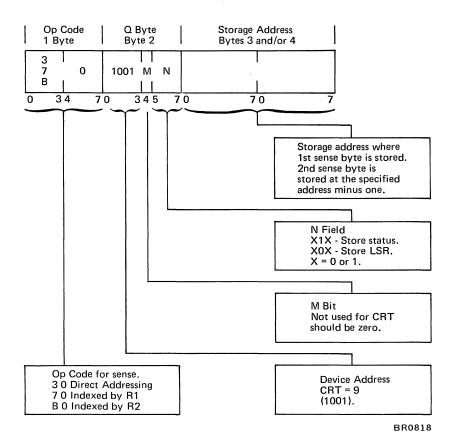

# Data Recorder and CRT Sense Instruction

| Op Code                  | Q    | Code | )     | Address                              | Op Code Q Code D1                                                                                                                                                                                                                                                                                                                            | Byte 1 = Operand Address Byte 2 = Operand Address -1 |  |  |  |  |  |  |  |

|--------------------------|------|------|-------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|--|--|--|--|